# Projet S.P. R.O

Franck GASTALDI

Journées RHIC France - 28 juin 2005

#### Plan

- Caractéristiques de la carte S.P.I.R.O

- Conception du prototype I

- Banc de tests

- Conception du prototype II

- État d'avancement

- Calendrier

- État des contributions extérieures au LLR :

- ☐ La mécanique,

- Les pixels,

- Le bus pixel,

- Les FEM

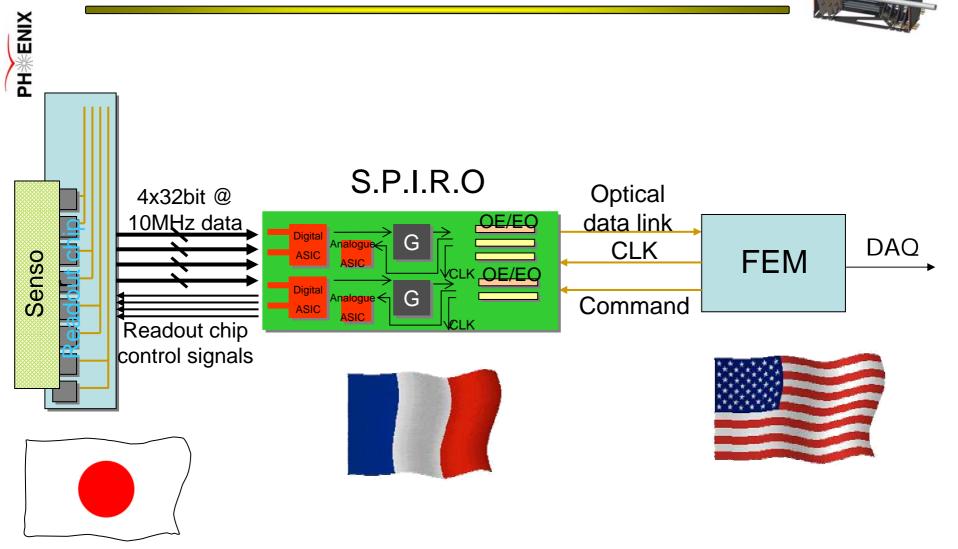

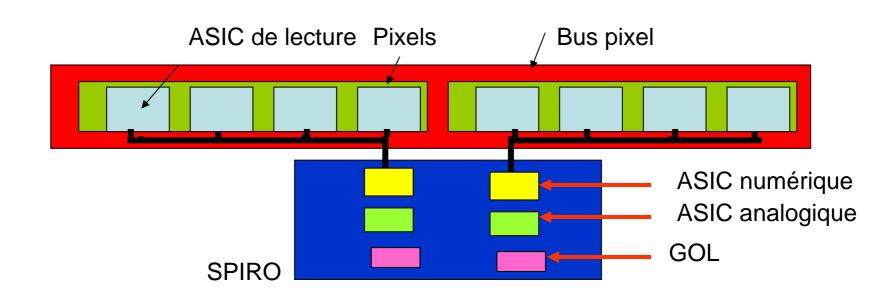

# Chaîne électronique

# PH\*ENIX LM

# Caractéristiques de la carte S.P.I.R.O (1/3)

- S.P.I.R.O signifie Silicon Pixel Interface Read-Out

- S.P.I.R.O est situé proche des échelles et éloigné des FEMs.

- Nous devons produire 100 cartes (60 + 40 spares)

- Principales fonctions

- Recevoir les données des échelles de pixels

- Lecture d'une ½ échelle soit 8x (256x32) = 65536 voies/carte

- Organiser les données au format PHENIX

- Transmettre les données via fibres optiques

- Caractéristiques électriques

- 4x32 bits @10MHz (données)

- 2 liens optiques @ 1.6Gbits/s

- 2 liens commandes optiques

- 1 lien optique horloge (40 MHz)

# Caractéristiques de la carte S.P.I.R.O (2/3)

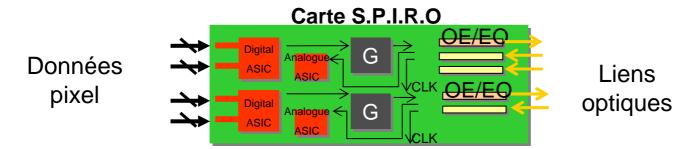

- Composants principaux

- ASIC numérique

- ☐ Envoie les commandes vers les ASICs de lecture des pixels

- ☐ Reçoit les données de ces mêmes ASICs

- ☐ Met en forme les données pour les transmettre via liens optiques

- Composant GOL (Gigabit Optical Link)

- ☐ Transmet les données à 1.6 Gbit/s

- ASIC analogique

- ☐ Fournit les tensions de référence vers les ASICs de lecture des pixels

- Modules optique

- ☐ Diode laser (VCSEL) pour l'émission

- □ Diode PIN pour recevoir les commandes et l'horloge issues des FEMs

# Caractéristiques de la carte S.P.I.R.O (3/3)

- Les défis de S.P.I.R.O.

- ■La carte doit être la plus petite possible

- ☐ Taille optimale: 10x15 cm doit tendre vers 10x10 cm

- ☐ Haute fiabilité car une carte gère 64536 canaux et maintenance difficile (Shut-Down pour maintenance)

- ☐ Faible bruit

- Production de 6 cartes du type prototype I

- □3 Japon, 1 USA, 2 LLR

# Conception du prototype - I

- □ Le Prototype I avec ASIC numérique d'ALICE

- ☐ Cet ASIC ne remplit pas le cahier des charges de PHENIX

- Champs dans le format de données

- Signaux de contrôle par rapport au protocole envisagé (Ethernet)

- Programmation d'un FPGA répondant aux fonctionnalités manquantes :

- Champs avec calcul de parité et compteur de trigger

- ☐ Envoi des signaux de contrôle du GOL pour un codage 8b/10b

- Concevoir un PCB le plus proche possible de la version finale

#### Banc de tests (1/2)

- Objectifs :

- Concevoir un banc de tests pour l'ensemble des prototypes et la production

- ☐ Tests de qualifications des liens optiques (taux d'erreur, jitter)

- Moyens:

- Un générateur de signaux simulant les données pixel et de commandes

- Un système pour l'acquisition

- Un système pour les liens optiques

#### Banc de tests (2/2)

- Solutions

- Pour le générateur de signaux

Nous utiliserons une solution commerciale

PXI de National Instruments

- □ Pour le lien optique Nous utiliserons une carte d'évaluation contenant un FPGA avec transceiver optique

- État actuel

- Le châssis PXI est au LLR depuis mai

- Les premiers tests ont été effectués sur l'ASIC numérique version I

- Les premières commandes ont été décodées

# Conception du prototype - II

#### **Avant production finale**

- Conception de la carte avec l'ASIC version II

- Calcul de la parité

- Compteur de trigger

- Signaux de contrôle du GOL

- Pas de FPGA sur cette carte

- Conception du PCB avec ses dimensions finales

#### Plan B :

En cas de problèmes majeurs de fonctionnement, nous envisagerons une solution « tout FPGA »

#### Où en sommes-nous?

- Banc de tests présent au LLR

- Les composants de la carte sont en saisie librairie pour la schématique

- Un premier pré-positionnement est en cours, les dimensions finales pourraient d'ores et déjà être atteintes

- Le FPGA a été sélectionné

- Le code VHDL est en développement

- L'ASIC version I est sous tests

#### Que reste-t-il à faire ?

#### Prochains mois ou en cours

- Prototype I

- ☐ Finir la schématique de la carte

- Simuler le FPGA

- Démarrer la conception de la carte

- Sélectionner les composants optiques et le type de connecteur

- Banc de tests

- Continuer la mise en œuvre du banc de tests

- Informatique de pilotage

- Développement du contenu du FPGA pour qualification du lien optique

- Choix du sous-traitant pour la fabrication et le câblage du prototype I (6 cartes à fabriquer)

- Réception des composants fournis par le Japon via le CERN

# Calendrier

| Fév. – Juil. 2005 | Conception du prototype I                                                               |

|-------------------|-----------------------------------------------------------------------------------------|

| JuilSept. 2005    | Production de 6 cartes                                                                  |

| Sept. 2005        | Premier test de S.P.I.R.O                                                               |

| Oct. 2005         | Tests en cosmiques avec 3 échelles (3 S.P.I.R.O au Japon) Tests FEM (1 S.P.I.R.O , USA) |

| Nov. 2005         | Conception du prototype II avec l'ASIC version II                                       |

| Début 2006        | Test en faisceau au KEK                                                                 |

| Jan. 2006         | Production des cartes version II                                                        |

| Fev. 2006         | Premier test de S.P.I.R.O version II                                                    |

| ~ Mi 2006         | Début de la production des 100 cartes                                                   |

# État d'avancement dans la collaboration

- □ La mécanique

- Les pixels

- Le bus pixel

- Le FEM

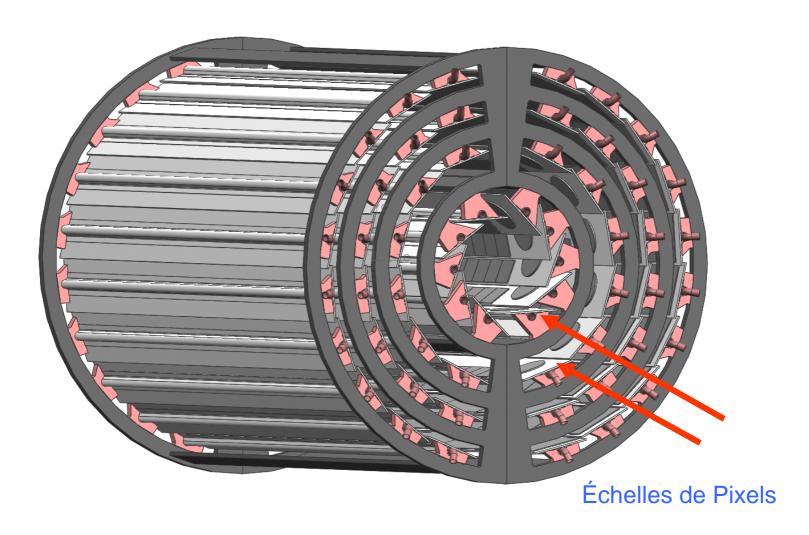

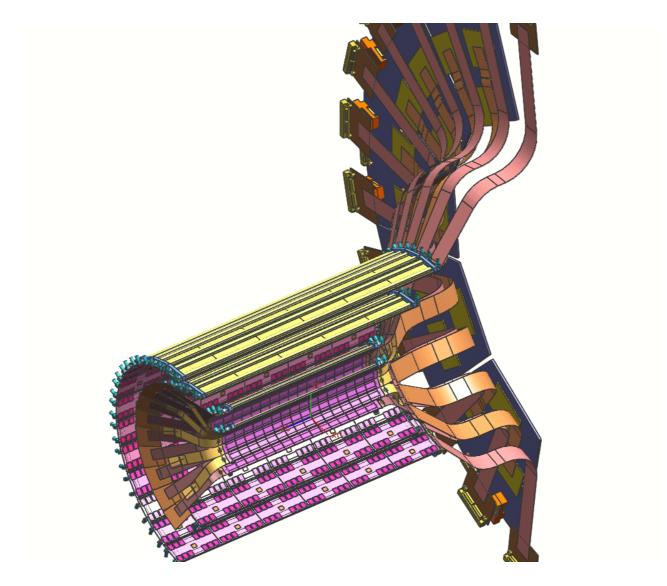

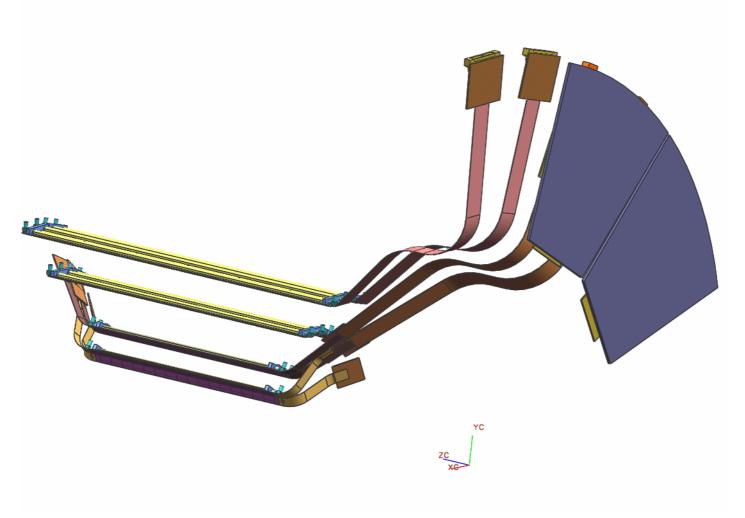

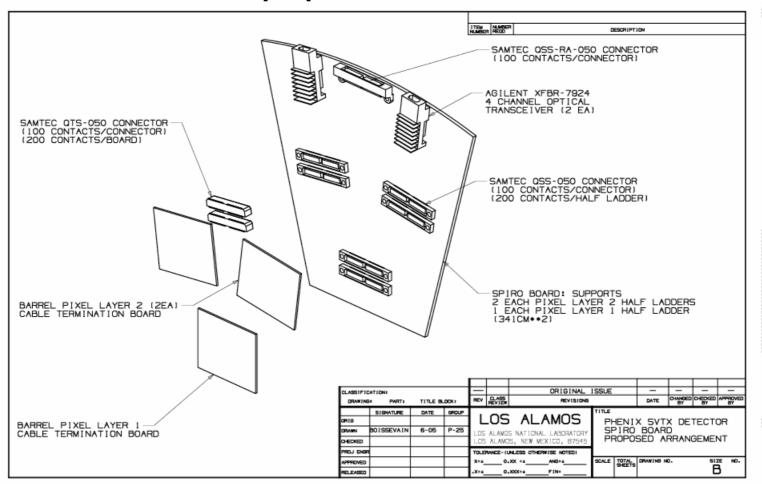

# La mécanique (Los Alamos)

# La chaîne de lecture

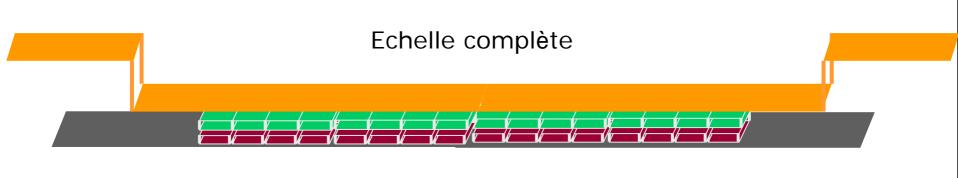

# Échelle – bus – support S.P.I.R.O

# Support et emplacement des cartes S.P.I.R.O

# Ceci est une proposition de Los Alamos

# LES PIXELS (RIKEN)

- Fin mars, 2 échelles ont été livrées au CERN

- testées et fonctionnelles

- Fin juin, 8 seront disponibles

- Fin 2005, 12 seront disponibles

- Le planning 2006 sera évoqué en septembre 2005

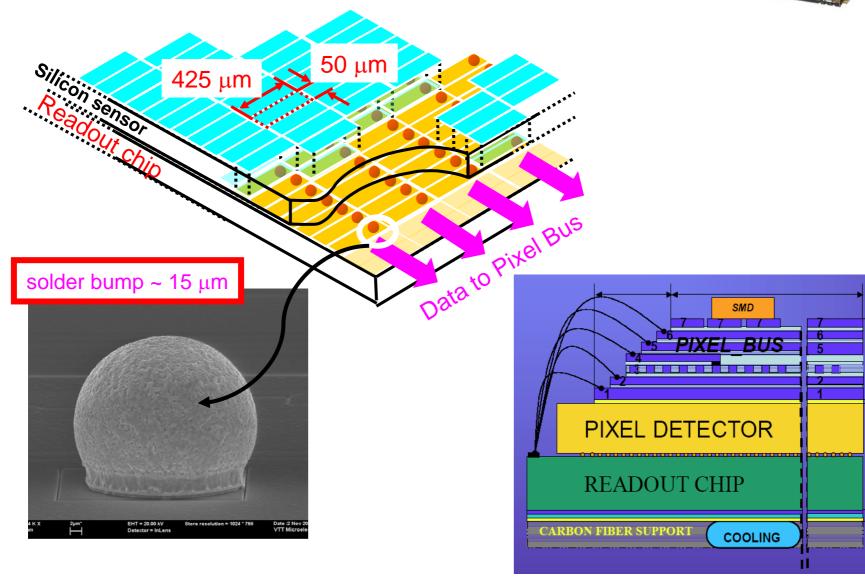

# Aperçu du collage et du bump bonding

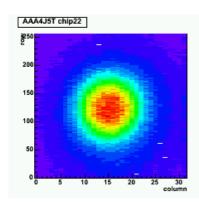

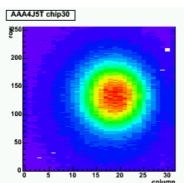

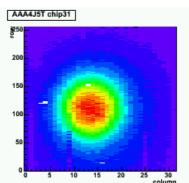

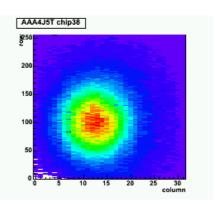

# Tests de 2 échelles avec une source à RIKEN

Journées RHIC France Franck GASTALDI

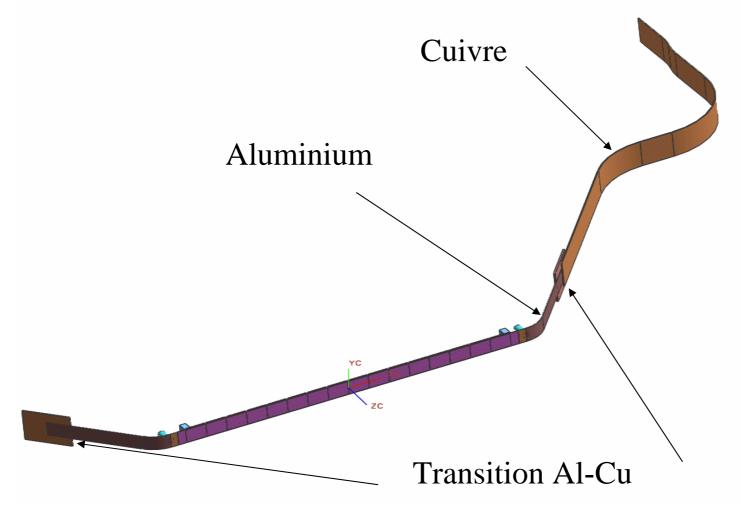

# Conception du bus pixel (RIKEN)

- Largeur du bus 15mm

- Longueur 10cm (pixel) + 15cm(extension)

- Bus Cu fabriqué ce mois-ci

- Bus Al fabriqué par la suite

- ☐ HT (<100V) est isolée des autres lignes

# Ensemble bus pixel connecté sur une échelle

# FEM (Front End Module) (StonyBrook)

Présentation de Harry Thermann au BNL June vertex meeting

- Code du FPGA en développement pour réception 1.6Gb/s

- Extraction du trigger par "Fast Or"

- Interface avec S.P.I.R.O

- Planning:

Conception PCB début Jun. 22, 2005

Fabrication Sep. 12, 2005

Tests Oct. 5, 2005

Interface avec SPIRO Oct. 17, 2005

- Cahier des charges

- ☐ Fiabilité maximum pour une taille minimum

- Campagne de tests importante

- Délais à respecter pour le prototype I

- Valider le fonctionnement de la carte

- Permettre le test préliminaire du FEM des Américains

- ☐ Permettre le test des échelles et du bus pixel des Japonais

- Très bonne collaboration triangulaire : Japon, France, USA