The GLAST experiment at SLAC

# **The GLT Electronics Module**

**Electronics group**

# **Programming ICD specification**

Document Version: Document Issue: Document Edition: Document Status: Document ID: Document Date: 2.7 1 English Under release control LAT-TD-01545-02 March 16, 2005

This document has been prepared using the Software Documentation Layout Templates that have been prepared by the IPT Group (Information, Process and Technology), IT Division, CERN (The European Laboratory for Particle Physics). For more information, go to http://framemaker.cern.ch/.

## Abstract

A conceptual design of the GEM (GLT Electronics Module) and the role it plays within the LAT Trigger System is described. The GEM is the electronic realization of the Global (GLT) Trigger. Its programmatic interface, used to both configure and monitor its behaviour, is defined and described. Last, the contribution of the GEM to the information contained within an event is defined and described.

### Hardware compatibility

This document assumes the following hardware revisions:

**TEM:** Version TBD

### **Intended** audience

This document is intended principally as a guide for the *developer* and *users* of the GLT Electronics Module (GEM). Users include:

- Developers of the sub-system electronics which interface with the GEM

- Developers of Flight-Software

- Developers of I&T (Integration and Test) based systems

All readers of this document are expected to be familiar with the concepts described in [1] and indeed, most the references described within.

## **Conventions used in this document**

Certain special typographical conventions are used in this document. They are documented here for the convenience of the reader:

- Field names are shown in bold and italics (*e.g.*, *respond* or *parity*).

- Acronyms are shown in small caps (*e.g.*, SLAC or TEM).

- Hardware signal or register names are shown in Courier bold (*e.g.*, RIGHT\_FIRST or LAYER\_MASK\_1)

### References

- 1 "LAT Inter-module Communications A reference manual," Michael Huffer, LAT-TD-00606.

- 2 "Event Builder Module Programming ICD specification," Michael Huffer, LAT-TD-01546.

- 3 "Command/Response Unit Programming ICD specification," Michael Huffer, LAT-TD-01547.

- 4 *Actel* data sheet for RadTolerant FPGAs for Space Applications (RT54SX-S).

- 5 "GASU Based Teststands A hardware and software Primer," Michael Huffer, LAT-TD-03664.

- 6 "Tower Electronics Module Programming ICD specification," Michael Huffer, LAT-TD-00605.

- 7 "Specification of the Glast Tracker Readout Controller Electronics (GTRC)," Jeff Olsen, LAT-SS-00170.

- 8 "Large Area Telescope (LAT) Instrument-Spacecraft Interface Requirements," 433-IRD-0001.

Note: For additional resources, refer to the LAT Electronics, DAQ Critical Design Requirements List. On the LAT Electronics, Data Acquisition & Instrument Flight Software page (http://www-glast.slac.stanford.edu/Elec\_DAQ/Elec\_DAQ\_home.htm), click Hardware and then click List of all documents.

## **Document Control Sheet**

| Document   | Title:               | The GLT Electronics Modul                                          | e Programmir | ng ICD specification |

|------------|----------------------|--------------------------------------------------------------------|--------------|----------------------|

|            | Version:             | 2.7                                                                |              |                      |

|            | Issue:               | 1                                                                  |              |                      |

|            | Edition:             | English                                                            |              |                      |

|            | ID:                  | LAT-TD-01545-02                                                    |              |                      |

|            | Status:              | Under release control                                              |              |                      |

|            | Created:             | February 9, 2002                                                   |              |                      |

|            | Date:                | March 16, 2005                                                     |              |                      |

|            | Access:              | V:\GLAST\Electronics\Design Documents\GEM\v2.7\Frontmat-<br>ter.fm |              |                      |

|            | Keywords:            | GLT Electronics Module GEM                                         |              |                      |

| Tools      | DTP System:          | Adobe FrameMaker                                                   | Version:     | 6.0                  |

|            | Layout<br>Template:  | Software Documentation<br>Layout Templates                         | Version:     | V2.0 - 5 July 1999   |

|            | Content<br>Template: |                                                                    | Version:     |                      |

| Authorship | Coordinator:         | Michael Huffer                                                     |              |                      |

|            | Written by:          | Michael Huffer                                                     |              |                      |

Table 1 Document Control Sheet

#### Table 2 Approval sheet

| Name           | Title                          | Signature | Date |

|----------------|--------------------------------|-----------|------|

| Gunther Haller | LAT Chief Electronics Engineer |           |      |

| JJ Russell     | Flight Software Lead           |           |      |

## **Document Status Sheet**

| Title:  | The GLT H | Electronics Mo | dule Programming ICD specification                                                                                                                                                                                                                                    |

|---------|-----------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ID:     | LAT-TD-0  | 1545-02        |                                                                                                                                                                                                                                                                       |

| Version | Issue     | Date           | Reason for change                                                                                                                                                                                                                                                     |

| 1.0     | 1         | 5/29/2002      | Initial draft                                                                                                                                                                                                                                                         |

| 1.1     | 1         | 6/25/2002      | Incorporated comments from Curt, Gunther, JJ, and Tony                                                                                                                                                                                                                |

| 1.2     | 1         | 1/07/2003      | Major changes, moving ever onwards towards a <i>real</i> document.<br>This release is only so JJ, Tony, and Jozesf can have a look- see.                                                                                                                              |

| 1.3     | 1         | 2/17/2003      | Still moving onwards I now believe that chapters 2, 3, and 4 are substantially correct. This release is only so JJ, Tony, James, and Jozesf can have a look-see.                                                                                                      |

| 1.4     | 1         | 2/20/2003      | Mostly, fixing typos as result of comments by James and JJ.<br>Changed measurement of deadtime to measurement of live-<br>time. Increased time-base counter to 25 bits and decreased<br>1-PPS counter to 7 bits. Increased rate of periodic trigger to 160<br>KHZ.    |

| 1.5     | 1         | 4/22/2003      | Effectively, the entire document has been re-written. Lots of detail added on the Trigger <i>System</i> and role the GEM has within this system. However, the GEM itself, has not changed that much. Here are the highlights:<br>— re-defined window width definition |

|         |           |                | — added version identification (configuration register)                                                                                                                                                                                                               |

|         |           |                | <ul> <li>re-thought and completely revamped whole idea of<br/>"bound" and "free-run modes". Now moved to control<br/>over periodic trigger.</li> </ul>                                                                                                                |

|         |           |                | <ul> <li>periodic trigger rates modified (and explained)</li> </ul>                                                                                                                                                                                                   |

|         |           |                | <ul> <li>added <i>inhibit</i> field to Message engine. Changed definition of pre-scalers.</li> </ul>                                                                                                                                                                  |

| 1.6     | 1         | 5/02/2003      | Mostly, fixing typos as result of comments by James and JJ.<br>Changed measurement of deadtime to measurement of live-<br>time. Increased time-base counter to 25 bits and decreased<br>1-PPS counter to 7 bits. Increased rate of periodic trigger to 160<br>KHZ.    |

#### Table 3 Document Status Sheet

| Table 3 | <b>Document Status Sheet</b> |

|---------|------------------------------|

|---------|------------------------------|

| 1.7 | 1 | 9/22/2003 | Changes to reflect the reality of actually building the "beast".<br>The important changes are in the register interface. They<br>include:<br>— re-ordering of the registers in the controller<br>— added new register block (the WINDOW block), moved<br>WINDOW_OPEN_MASK register and WINDOW_WIDTH<br>fields from CONFIGURATION register to this block.<br>— added new fields to CONFIGURATION register. |

|-----|---|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     |   |           | <ul> <li>completely redefined meaning of fields of registers<br/>within the INPUT_ENABLE block.</li> </ul>                                                                                                                                                                                                                                                                                                |

| 1.8 | 1 | 2/10/2004 | Changes to reflect the reality of actually building the "beast".<br>The important changes are in the register interface. They<br>include:                                                                                                                                                                                                                                                                 |

|     |   |           | <ul> <li>re-ordering of the registers in the controller</li> </ul>                                                                                                                                                                                                                                                                                                                                        |

|     |   |           | <ul> <li>added new register block (the WINDOW block), moved<br/>WINDOW_OPEN_MASK register and WINDOW_WIDTH<br/>fields from CONFIGURATION register to this block.</li> </ul>                                                                                                                                                                                                                               |

|     |   |           | <ul> <li>added new fields to CONFIGURATION register.</li> </ul>                                                                                                                                                                                                                                                                                                                                           |

|     |   |           | <ul> <li>completely redefined meaning of fields of registers<br/>within the INPUT_ENABLE block.</li> </ul>                                                                                                                                                                                                                                                                                                |

|  | Table 3 | <b>Document Status Sheet</b> |

|--|---------|------------------------------|

|--|---------|------------------------------|

|     |   | 1         |                                                                                                                                                                                                                                                                                                                           |

|-----|---|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.0 | 1 | 3/08/2004 | Many, many, changes to reflect "as built". These include (in no particular order):                                                                                                                                                                                                                                        |

|     |   |           | <ul> <li>Incorporated GXH's comments (of a year ago!)</li> </ul>                                                                                                                                                                                                                                                          |

|     |   |           | — <i>All</i> registers are now 32-bits                                                                                                                                                                                                                                                                                    |

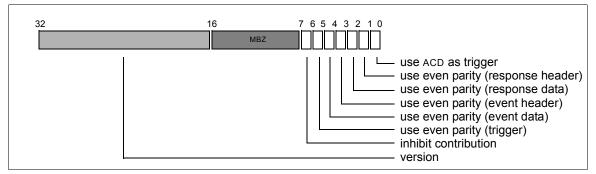

|     |   |           | <ul> <li>Configuration register completely different. More<br/>control over "dummying" up parity. Removed mixing<br/>and matching of modules, as this is no longer supported<br/>by the GASU. New version information, to reflect the fact<br/>that the GEM has three FPGAs, each with their own<br/>lifetime.</li> </ul> |

|     |   |           | <ul> <li>Added field in Configuration register to inhibit production of GEM's event contribution.</li> </ul>                                                                                                                                                                                                              |

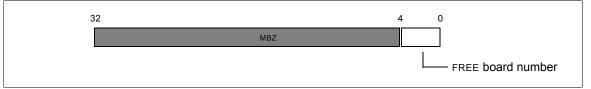

|     |   |           | <ul> <li>Made connection between ACD naming conventions and<br/>FREE board, tile number etc. See new appendix.</li> </ul>                                                                                                                                                                                                 |

|     |   |           | <ul> <li>Cleaned up notation. Trigger Summary is now Condition<br/>Summary. Template-X are now Engine-X. Indices-x are<br/>now Conditions-X.</li> </ul>                                                                                                                                                                   |

|     |   |           | <ul> <li>Eliminated so-called "trigger order" in ROI and enable<br/>definition registers. Registers are now arranged in FREE<br/>board order.</li> </ul>                                                                                                                                                                  |

|     |   |           | <ul> <li>Entire handling of statistics counter(s) has completely changed.</li> </ul>                                                                                                                                                                                                                                      |

|     |   |           | <ul> <li>New counters for counting singles rates on ACD tiles.</li> </ul>                                                                                                                                                                                                                                                 |

|     |   |           | <ul> <li>Periodic trigger rate register is now specified as a prescale, rather then an exponent.</li> </ul>                                                                                                                                                                                                               |

|     |   |           | <ul> <li>Renamed "busy" counter to "discarded" counter.</li> </ul>                                                                                                                                                                                                                                                        |

|     |   |           | <ul> <li>Inverted "busy" counter and "prescaled" counter in event data.</li> </ul>                                                                                                                                                                                                                                        |

|     |   |           | <ul> <li>Changed default sense of "periodic mode register" in<br/>order to have periodic condition come up disabled by<br/>default.</li> </ul>                                                                                                                                                                            |

|     |   |           | <ul> <li>Window width register used to have built-in offset of<br/>four (4) clock tics. This is no longer true. Beware: Do not<br/>program this register with a value of <i>zero</i>.</li> </ul>                                                                                                                          |

|     |   |           | <ul> <li>Added one more piece of information to the GEM's event<br/>contribution. This piece of information computes the<br/><i>delta</i> time between events.</li> </ul>                                                                                                                                                 |

|     |   |           | <ul> <li>By mistake, exposed high order bit of destination<br/>address, used in configured engines. This field is always<br/>an implied one (1), as events can only be sent to a master<br/>on the event fabric. Field is now <i>Read-Only</i>.</li> </ul>                                                                |

|     |   |           | Updated fonts.                                                                                                                                                                                                                                                                                                            |

| Table 3 | <b>Document Status Sheet</b> |

|---------|------------------------------|

|---------|------------------------------|

| 2.1 | 1 | 4/22/2004 | <ul> <li>Minor changes. Mostly reflect fixing typos and the fact that the structure of the configuration register changed and a documentation of the tile mapping for the "first article". The changes include: <ul> <li>structure of CONFIGUARTION register changed (removed 1-PPS selection).</li> <li>PERIODIC_TRIGGER_RATE register changed. Counter is actually 24 bits rather then 16 bits.</li> <li>Mapping of ROI generator (table 15) was documented incorrectly. Middle entries were shifted by one.</li> <li>Tile mapping for the "goofy" board (first ship) does not match documentation. This is fixed on the next layout as it required to many new wires on the current board (see appendix A).</li> </ul> </li> </ul> |

|-----|---|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     |   |           | appendix Aj.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 2.1 | 2 | 4/23/2004 | Corrected some typos.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 2.2 | 1 | 4/29/2004 | This version represents the changes in going from the "first" generation GEM to the "second" generation GEM. There are three: First, as the new board has one more FPGA, the version structure has changed in the configuration register. Also, as this is a new board, the board revision number has been incremented, which will allow one to differentiate old boards from new boards. Second, exchanged the order of the ribbon tiles (500x and 600x) to make the tile mapping monotonically increasing. This changed both the ROI and tile enable registers (and appendix A). Third, the tower "busy" enables were moved to their own register (register 17) rather then sharing                                                 |

| 2.2 | 3 | 5/18/2004 | Corrected some typos.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 2.2 | 5 | 6/10/04   | Updated references and PDF TOC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Table 3 Document Status Shee |

|------------------------------|

|------------------------------|

|     | ument Statu | e encor  |                                                                                                                                                                                                                                                                                                                                                   |

|-----|-------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.3 | 1           | 9/01/04  | Updated to reflect new hardware functionality Added new CNO counters. Added new condition: the external trigger.                                                                                                                                                                                                                                  |

| 2.4 | 1           | 10/18/04 | Some new functionality and re-definition of the tracker <i>not</i> vetoed condition (which has always been wrong). These changes are reflected in a hardware version number of five (5) for both the scheduler and TAM. The ROI version is "don't care". The changes include:<br>— Added access to 1-PPS counter and register (see Section 2.6.4) |

|     |             |          | <ul> <li>Reused the sent event contribution and replaced this contribution with a measurement of the relative arrival times of the conditions present in the event. (see Section 4.13). Note: this change is <i>not</i> back-ward compatible.</li> </ul>                                                                                          |

|     |             |          | <ul> <li>Added enable for external trigger condition. This feature was omitted when I added the external condition. Note: As the external condition, was by default previously <i>enabled</i> and is now by default <i>disabled</i>, this change is <i>not</i> backwardly compatible. (see Section 2.6.3)</li> </ul>                              |

|     |             |          | <ul> <li>The tracker <i>not</i>-vetoed definition was incorrect. Nothing<br/>is changed in the hardware, however, the condition has<br/>been renamed to tracker vetoed. (see Section 1.7.1 and<br/>Figure 30)</li> </ul>                                                                                                                          |

|     |             |          | <ul> <li>Added on more bit of range to livetime counter (now 25 bits)</li> </ul>                                                                                                                                                                                                                                                                  |

| 2.5 | 1           | 01/26/05 | The changes are:<br>— Added access to the GEM's internal time-base (see<br>Section 2.6.5)                                                                                                                                                                                                                                                         |

|     |             |          | <ul> <li>For some, unidentified reason, I never updated the description of the Periodic Trigger Rate Register (see Section 2.3.3.1) and Periodic Limit Register. (see Section 2.3.3.3). Don't know why - its been that way in the hardware forever. Thank's Gregg for pointing this out.</li> </ul>                                               |

| 2.6 | 1           | 03/01/05 | The changes are:<br>— Added new register to count potential window turns in<br>"dead zone" (see Section 2.6.1.2)                                                                                                                                                                                                                                  |

|     |             |          | <ul> <li>Least significant 8 bits of dead-zone counter are sampled<br/>and returned in event contribution (see Section 4.8).</li> </ul>                                                                                                                                                                                                           |

|     |             |          | <ul> <li>Added load descriptor for statistics block (was<br/>implemented in hardware and software, but never<br/>documented). See Section 3.5.</li> </ul>                                                                                                                                                                                         |

|     |             |          | <ul> <li>Removed dataless command descriptor for statistics<br/>block (was never implemented in hardware or software,<br/>and is no longer required). See Section 3.5.</li> </ul>                                                                                                                                                                 |

|     |             |          | <ul> <li>Corrected (some) typos and added a little more<br/>explanation of a window (but still needs more).</li> </ul>                                                                                                                                                                                                                            |

| Table 3 | Document Status Sheet |

|---------|-----------------------|

|---------|-----------------------|

| 2.6 | 2 | 03/05/05 | Updated explanation of how statistics are actually reset (see Section 2.6.1).                                                                                                                                               |

|-----|---|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.7 | 1 | 03/16/05 | Added a new register in order to allow programmatic control<br>of the external trigger condition (see Section 2.3.7). Corrected<br>some typos and added additional clarification of the dead-zone<br>(see Section 2.6.1.2). |

# **Table of Contents**

| Abstract                                   | .3 |

|--------------------------------------------|----|

| Hardware compatibility                     | .3 |

| Intended audience                          | .3 |

| Conventions used in this document          | .3 |

| References                                 | .4 |

| Document Control Sheet                     | .5 |

| Document Status Sheet                      | .6 |

| List of Figures                            | 17 |

| List of Tables.                            | 23 |

| Chapter 1                                  |    |

| Principles of operation                    |    |

| 1.1 Overview                               |    |

| 1.2 Physical partitioning of the GEM       | 28 |

| 1.3 Trigger Sources                        | 32 |

| 1.3.1 The ACD                              | 32 |

| 1.3.2 The Tower                            | 33 |

| 1.3.2.1 The Calorimeter                    | 34 |

| 1.3.2.2 The Tracker                        | 36 |

| 1.3.3 Internal                             | 40 |

| 1.4 Trigger Inputs                         | 41 |

| 1.4.1 Tiles, Vetos and Region of Interests | 42 |

| 1.5 The Trigger Window                     |    |

| 1.5.1 The ROI Signal                       | 45 |

| 1.5.2 The Tracker Condition                                      | 46 |

|------------------------------------------------------------------|----|

| 1.5.3 The Calorimeter (Low Energy) Condition                     | 46 |

| 1.5.4 The Calorimeter (High Energy) Condition                    | 46 |

| 1.5.5 The CNO Condition                                          | 47 |

| 1.5.6 The Periodic Condition                                     | 47 |

| 1.5.7 The Solicited Condition                                    | 48 |

| 1.5.8 The External Condition                                     | 48 |

| 1.6 Forming the Trigger Vectors and Window Summary               | 48 |

| 1.6.1 The TKR Vector                                             | 49 |

| 1.6.2 The ROI Vector                                             | 50 |

| 1.6.3 The Calorimeter (Low Energy) Vector                        | 51 |

| 1.6.4 The Calorimeter (High Energy) Vector                       |    |

| 1.6.5 The CNO Vector                                             | 52 |

| 1.7 Forming a Condition Summary and resolving the Message Engine | 53 |

| 1.7.1 Forming the Condition Summary                              | 53 |

| 1.7.2 The Condition Summary                                      | 55 |

| 1.7.3 Looking up a Message Engine                                | 56 |

| 1.7.4 The Scheduling Engine                                      | 57 |

| 1.8 TAM Formation                                                | 58 |

| 1.8.1 The Message Engine                                         | 58 |

| 1.8.2 Making a trigger decision                                  | 59 |

| 1.8.3 The Sequence Register                                      | 60 |

| 1.8.4 Transmitting the TAM                                       | 61 |

| 1.8.5 Transmitting the Event Contribution                        | 62 |

| 1.8.6 Trigger Accept Message structure                           | 63 |

| 1.8.6.1 Trigger Context                                          | 64 |

| 1.8.6.2 Trigger sequencing                                       | 66 |

| 1.8.6.3 Trigger Command structure by subsystem                   | 69 |

| 1.9 The Timebase                                                 | 71 |

| 1.10 Veto Sample and Hold                                        | 72 |

| 1.11 Trigger System latency and timing                           | 72 |

| Chapter 2                                                        |    |

| Chapter 2<br>Registers                                           | 75 |

| 2.1 Introduction                                                 | 75 |

| 2.2 Conventions                                                  |    |

| 2.3 GEM controller registers                                     | 76 |

| 2.3.1 Configuration register                                     | 77 |

| 2.3.1.1 Version ID                                               |    |

| 2.3.2 Address register                                           |    |

| 2.3.3 Controlling the periodic trigger input                     |    |

| 2.3.3.1 Periodic Trigger Rate register                           |    |

|                                                                  |    |

|       | 2.3.3.2 Periodic mode register                |      | • | • |       | • | • | • | • | • | • | • | • | . 80  |

|-------|-----------------------------------------------|------|---|---|-------|---|---|---|---|---|---|---|---|-------|

|       | 2.3.3.3 Periodic Limit register               |      |   |   |       | • |   |   |   |   | • |   |   | . 80  |

|       | 2.3.4 Sequence register                       |      |   |   |       | • |   | • | • | • | • | • |   | . 81  |

|       | 2.3.5 Command/Response statistics regis       | ster |   |   |       | • |   | • | • | • |   | • |   | . 81  |

|       | 2.3.6 Event statistics register               |      |   |   |       | • |   | • | • | • | • | • |   | . 82  |

|       | 2.3.7 External condition delay register .     |      |   |   |       | • |   | • | • | • | • | • |   | . 82  |

| 2     | 2.4 Window registers                          |      |   |   |       |   |   |   |   |   |   |   |   | . 83  |

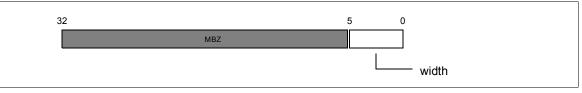

|       | 2.4.1 Window Width                            |      |   |   |       |   |   |   |   |   |   |   |   | . 83  |

|       | 2.4.2 Window Open Mask register               |      |   |   |       |   |   |   |   |   |   |   |   | . 83  |

| 2     | 2.5 The TAM Generator registers               |      |   |   |       |   |   |   |   |   |   |   |   | . 84  |

| 2     | 2.6 Trigger statistics                        |      |   |   |       |   |   |   |   |   |   |   |   | . 86  |

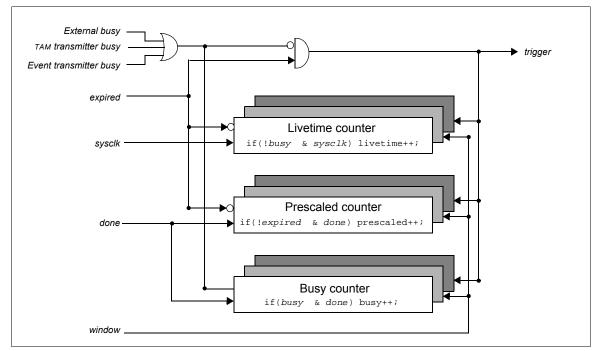

|       | 2.6.1 Performance counters                    |      |   |   |       |   |   |   |   |   |   |   |   | . 87  |

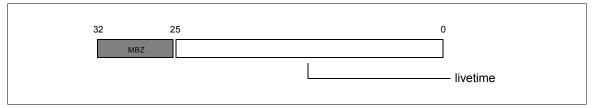

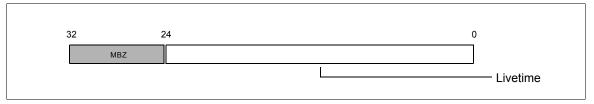

|       | 2.6.1.1 Livetime                              |      |   |   |       |   |   |   |   |   |   |   |   | . 87  |

|       | 2.6.1.2 Dead-Zoned                            |      |   |   |       |   |   |   |   |   |   |   |   | . 88  |

|       | 2.6.1.3 Window turns                          |      |   |   |       |   |   |   |   |   |   |   |   | . 88  |

|       | 2.6.2 Tile counters                           |      |   |   |       |   |   |   |   |   |   |   |   | . 89  |

|       | 2.6.3 CNO counters                            |      |   |   |       |   |   |   |   |   |   |   |   | . 90  |

|       | 2.6.4 1-PPS timers                            |      |   |   |       |   |   |   |   |   |   |   |   | . 91  |

|       | 2.6.5 Time-Base                               |      |   |   |       |   |   |   |   |   |   |   |   | . 92  |

| 2     | 2.7 Scheduler registers                       |      |   |   |       |   |   |   |   |   |   |   |   | . 92  |

| 2     | 2.8 Region-Of-Interest (ROI) Generator regist | ers  |   |   |       |   |   |   |   |   |   |   |   | . 94  |

|       | 2.8.1 The region used as a tower shadow       |      |   |   |       |   |   |   |   |   |   |   |   | . 96  |

|       | 2.8.2 The region used to form coincidence     | es   |   |   |       |   |   |   |   |   |   |   |   | . 96  |

| 2     | 2.9 Input enable registers                    |      |   |   |       |   |   |   |   |   |   |   |   | . 97  |

|       | 2.9.1 Tower enable registers                  |      |   |   |       |   |   |   |   |   |   |   |   |       |

|       | 2.9.2 ACD CNO enable register                 |      |   |   |       |   |   |   |   |   |   |   |   |       |

|       | 2.9.3 Tile enable registers                   |      |   |   |       |   |   |   |   |   |   |   |   | . 99  |

|       | 2.9.4 Tower busy enable register              |      |   |   |       |   |   |   |   |   |   |   |   |       |

|       | 2.9.5 External condition enable register      |      |   |   |       |   |   |   |   |   |   |   |   | . 106 |

|       |                                               |      |   |   |       |   |   |   |   |   |   |   |   |       |

| Chapt |                                               |      |   |   |       |   |   |   |   |   |   |   |   | 107   |

|       | nanding                                       |      |   |   |       |   |   |   |   |   |   |   |   |       |

| Ċ     | 3.1 Overview                                  |      |   |   |       |   |   |   |   |   |   |   |   |       |

| -     | 3.1.1 Conventions                             |      |   |   |       |   |   |   |   |   |   |   |   |       |

|       | 3.2 The GEM's access descriptor               |      |   |   |       |   |   |   |   |   |   |   |   |       |

| ť     | 3.3 Accessing the controller                  |      |   |   |       |   |   |   |   |   |   |   |   |       |

|       | 3.3.1 Dataless commands                       |      |   |   |       |   |   |   |   |   |   |   |   |       |

|       | 3.3.2 Load commands                           |      |   |   |       |   |   |   |   |   |   |   |   |       |

| _     | 3.3.3 Read commands                           |      |   |   |       |   |   |   |   |   |   |   |   |       |

| 3     | 3.4 Accessing the TAM Generator               |      |   |   |       |   |   |   |   |   |   |   |   |       |

|       | 3.4.1 Load commands                           |      |   |   |       |   |   |   |   |   |   |   |   |       |

|       | 3.4.2 Read commands                           | •    | • | • | <br>• | • | • | • | • | • | • | • | • | . 111 |

| 3.5 Accessing the Trigger Statistics block                                                             | 2  |

|--------------------------------------------------------------------------------------------------------|----|

| 3.5.1 Load commands                                                                                    |    |

| 3.5.2 Read commands                                                                                    | .3 |

| 3.6 Accessing the Scheduler                                                                            |    |

| 3.6.1 Load commands                                                                                    | 3  |

| 3.6.2 Read commands                                                                                    | 4  |

| 3.7 Accessing the ROI Generator                                                                        | 4  |

| 3.7.1 Load commands                                                                                    | 5  |

| 3.7.2 Read commands                                                                                    | 5  |

| 3.8 Accessing the Input Enables                                                                        | 6  |

| 3.8.1 Load commands                                                                                    | .6 |

| 3.8.2 Read commands                                                                                    | 7  |

| 3.9 Accessing the window block                                                                         | 7  |

| 3.9.1 Load commands                                                                                    | 7  |

| 3.9.2 Read commands                                                                                    | 8  |

|                                                                                                        |    |

| Chapter 4                                                                                              | ~  |

| <b>Events</b>                                                                                          |    |

| 4.1 The event contribution                                                                             |    |

| 4.2 The TKR Vector                                                                                     |    |

| 4.3 The ROI Vector                                                                                     |    |

| 4.4 The Calorimeter (Low Energy) Vector                                                                |    |

| 4.5 The Calorimeter (High Energy) Vector                                                               |    |

| 4.6 The CNO Vector                                                                                     |    |

| 4.7 Condition Summary                                                                                  |    |

| 4.8 Dead-Zone count                                                                                    |    |

| 4.9 The Tile List                                                                                      |    |

| 4.9.1 Correspondence between group and tile                                                            |    |

| 4.10 Sampled livetime                                                                                  | :7 |

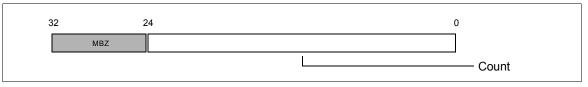

| 4.11 Sampled prescaled count                                                                           |    |

| 4.12 Sampled discarded count                                                                           | :8 |

| 4.13 Condition arrival times                                                                           |    |

| 4.14 Trigger Time                                                                                      | 9  |

| 4.15 Sampled 1-PPS time                                                                                | 9  |

| 4.16 Delta Event time                                                                                  | 0  |

| 4.17 Delta window open time                                                                            | 0  |

|                                                                                                        |    |

| Appendix A                                                                                             | 11 |

| Tile Mapping $\ldots$ | 1  |

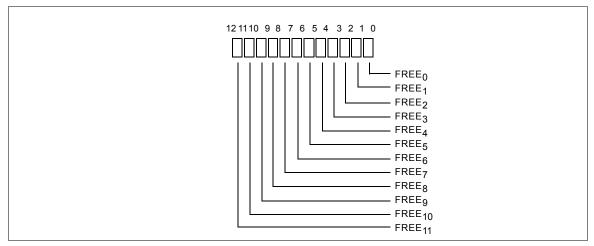

# **List of Figures**

| p. 27 | The GEM and its input and output interfaces                                                                                                                                                                                                     |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| p. 29 | Block diagram of the GEM and its trigger paths                                                                                                                                                                                                  |

| p. 30 | Block diagram of the GEM and its event paths                                                                                                                                                                                                    |

| p. 31 | Block diagram of the GEM and its Command/Response paths                                                                                                                                                                                         |

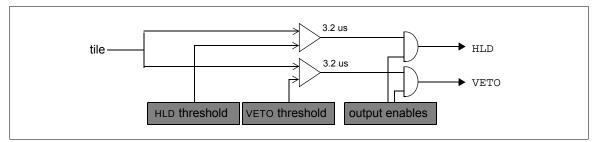

| p. 32 | Forming the HLD and VETO outputs on the GAFE                                                                                                                                                                                                    |

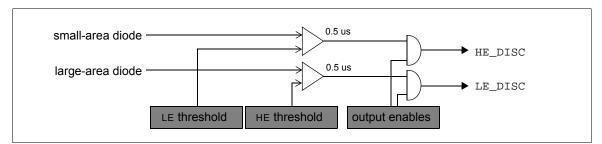

| p. 34 | Forming the LE_DISC and HE_DISC outputs on the GCFE                                                                                                                                                                                             |

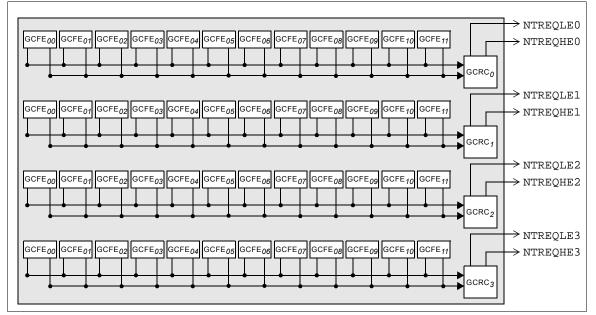

| p. 35 | Forming the eight Calorimeter Trigger Requests on the AFEE board                                                                                                                                                                                |

| p. 36 | Forming of the two Calorimeter Trigger Inputs on the TEM                                                                                                                                                                                        |

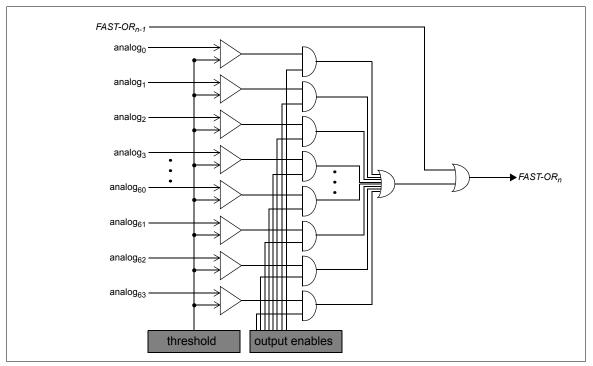

| p. 37 | Forming the FAST-OR output on the GTFE                                                                                                                                                                                                          |

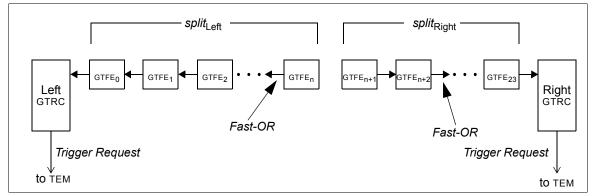

| p. 38 | Generation of Trigger Requests on an MCM                                                                                                                                                                                                        |

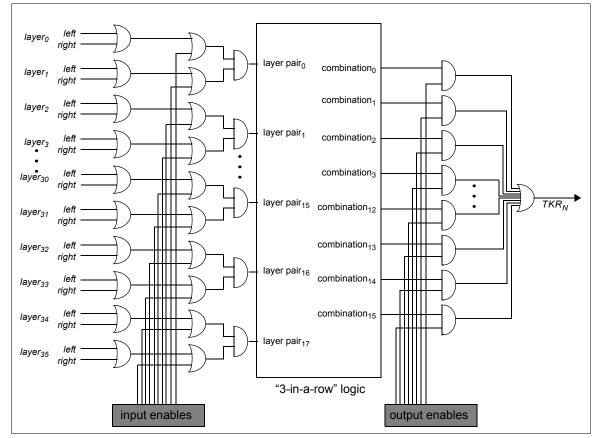

| p. 39 | Forming the TKR Trigger Input on the TEM                                                                                                                                                                                                        |

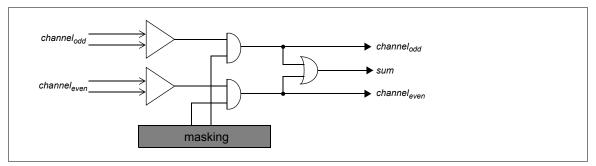

| p. 41 | One channel of the GLTC ASIC                                                                                                                                                                                                                    |

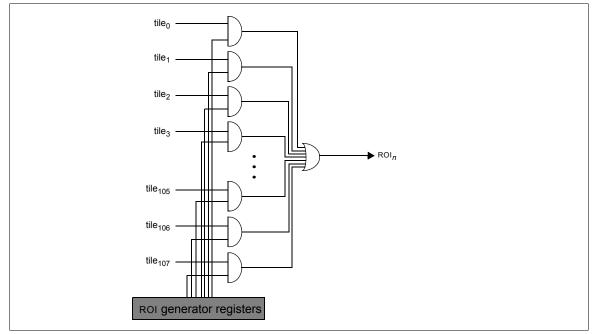

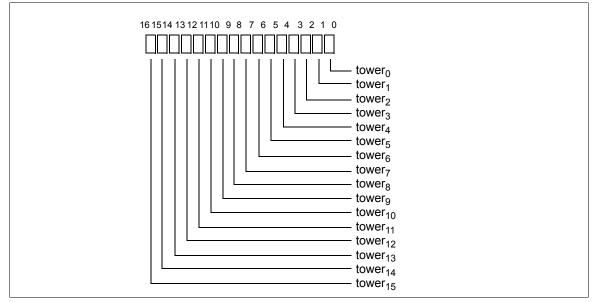

| p. 43 | Forming one of sixteen ROIS (Region of Interest)                                                                                                                                                                                                |

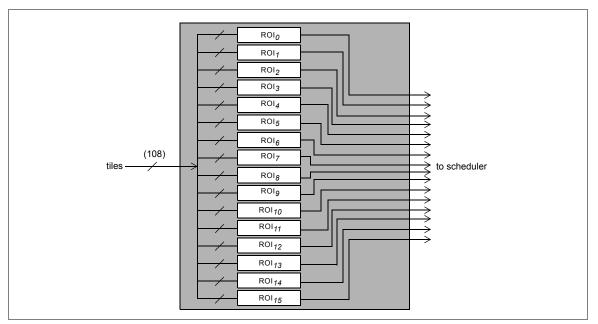

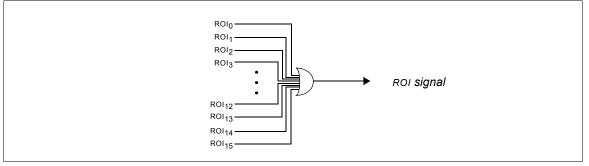

| p. 43 | Forming the sixteen ROI signals                                                                                                                                                                                                                 |

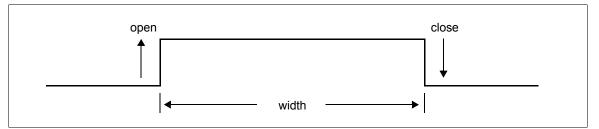

| p. 44 | The window signal                                                                                                                                                                                                                               |

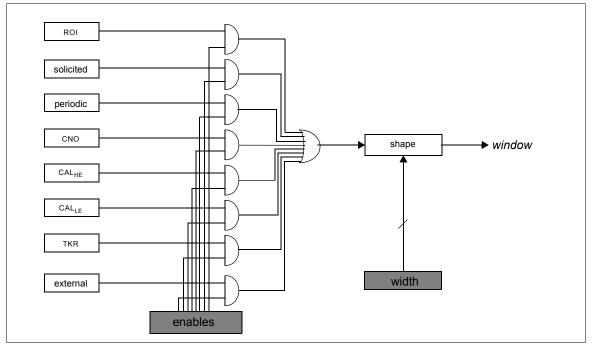

| p. 45 | Forming the window signal                                                                                                                                                                                                                       |

| p. 45 | Forming the Region-Of-Interest (ROI) Signal                                                                                                                                                                                                     |

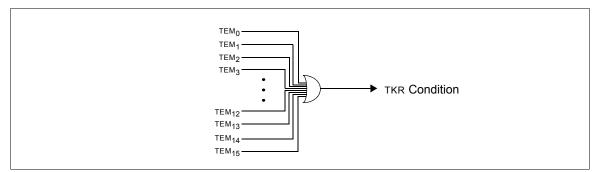

| p. 46 | Forming the Tracker (TKR) Condition                                                                                                                                                                                                             |

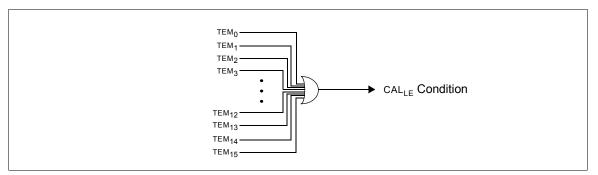

| p. 46 | Forming the Calorimeter (Low Energy) Condition                                                                                                                                                                                                  |

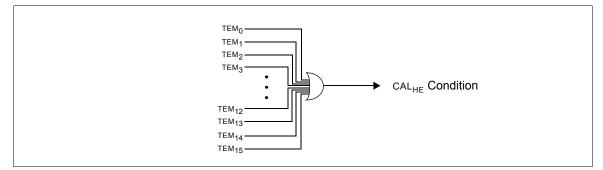

| p. 47 | Forming the Calorimeter (High Energy) Condition                                                                                                                                                                                                 |

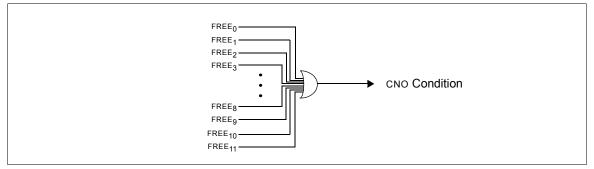

| p. 47 | Forming the CNO Open Window Signal                                                                                                                                                                                                              |

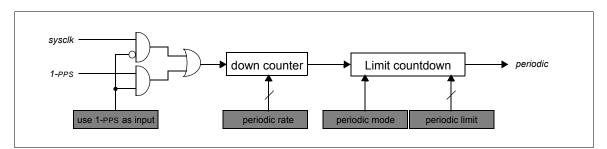

| p. 48 | Forming the Periodic Open Window Signal                                                                                                                                                                                                         |

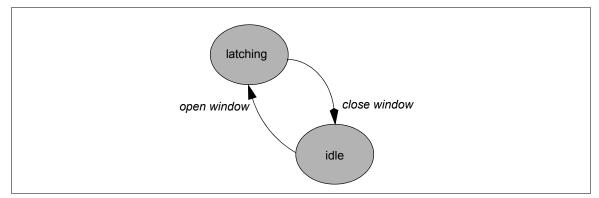

| p. 49 | The Generic Latching Engine                                                                                                                                                                                                                     |

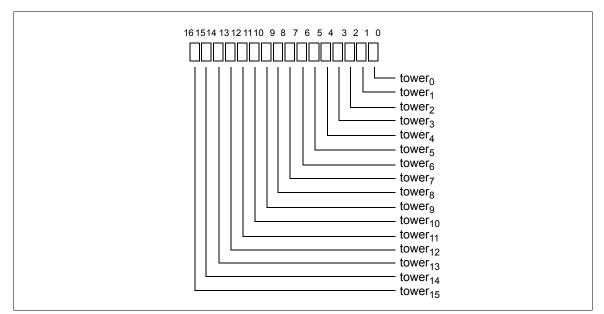

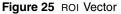

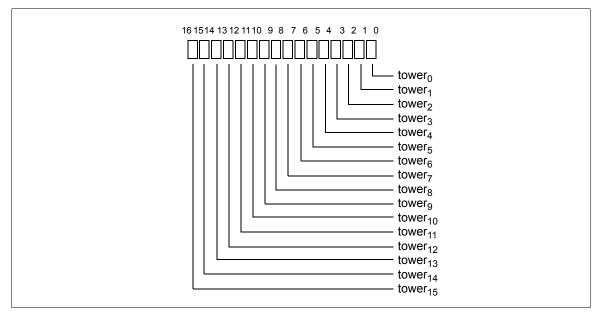

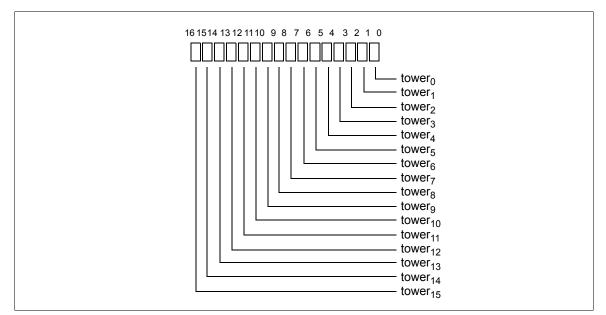

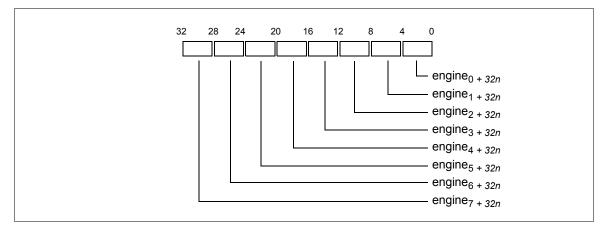

| p. 50 | TKR Vector                                                                                                                                                                                                                                      |

|       | p. 29<br>p. 30<br>p. 31<br>p. 32<br>p. 34<br>p. 35<br>p. 36<br>p. 37<br>p. 38<br>p. 39<br>p. 41<br>p. 43<br>p. 43<br>p. 43<br>p. 43<br>p. 43<br>p. 44<br>p. 45<br>p. 45<br>p. 45<br>p. 45<br>p. 46<br>p. 46<br>p. 47<br>p. 47<br>p. 48<br>p. 49 |

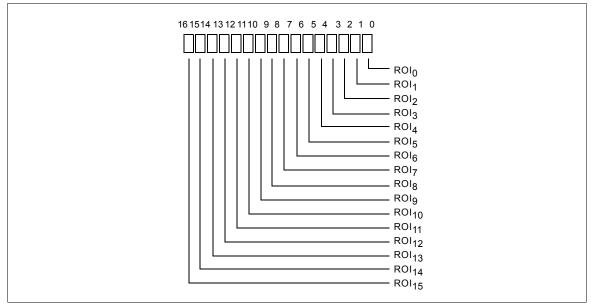

| Figure 25 | p. 50 | ROI Vector                                                         |

|-----------|-------|--------------------------------------------------------------------|

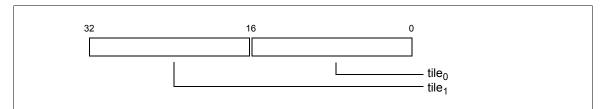

| Figure 26 | p. 51 | Calorimeter (Low Energy) Vector                                    |

| Figure 27 | p. 52 | Calorimeter (High Energy) Vector                                   |

| Figure 28 | p. 52 | CNO Vector                                                         |

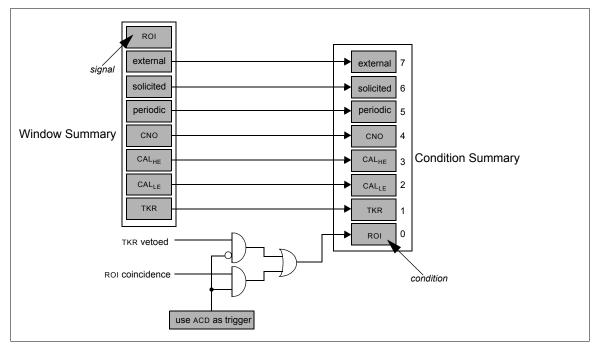

| Figure 29 | p. 54 | Forming the Condition Summary                                      |

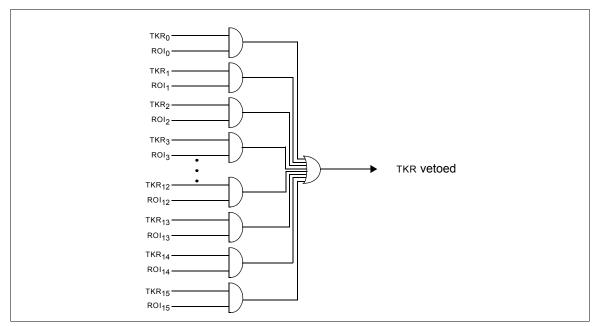

| Figure 30 | p. 54 | Forming the TKR (tracker) vetoed signal                            |

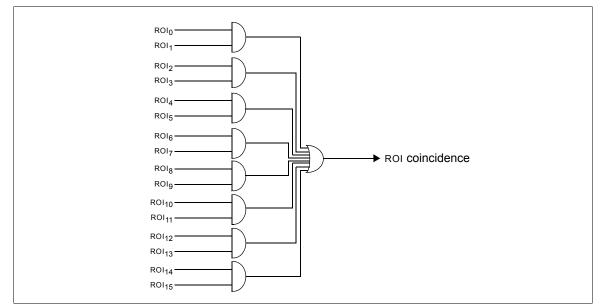

| Figure 31 | p. 55 | Forming the ROI coincidence signal                                 |

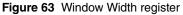

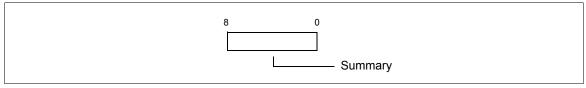

| Figure 32 | p. 55 | Condition Summary contribution to event                            |

| Figure 33 | p. 57 | Resolving the Condition Summary to a Message Engine                |

| Figure 34 | p. 58 | Block diagram of the TAM generator                                 |

| Figure 35 | p. 59 | Block diagram of a Message Engine                                  |

| Figure 36 | p. 60 | Making the Trigger decision                                        |

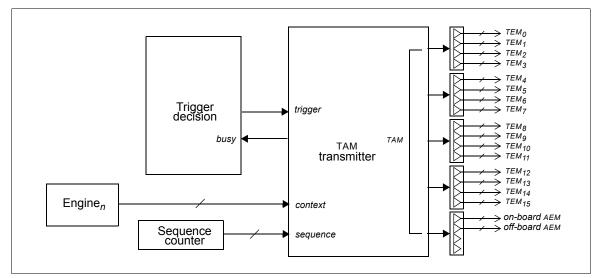

| Figure 37 | p. 61 | Block diagram of the TAM transmitter                               |

| Figure 38 | p. 62 | The TAM transmitter forming a message                              |

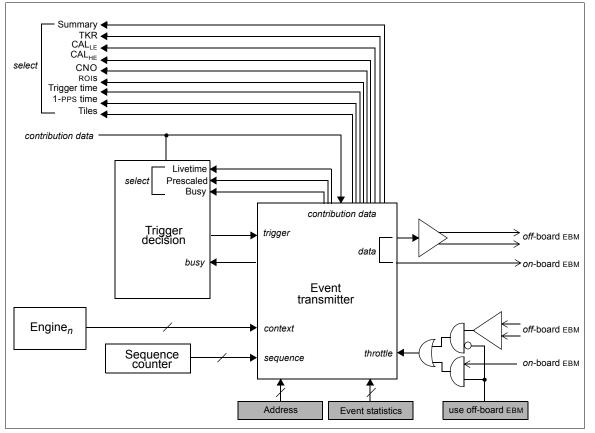

| Figure 39 | p. 63 | Block diagram of the Event transmitter                             |

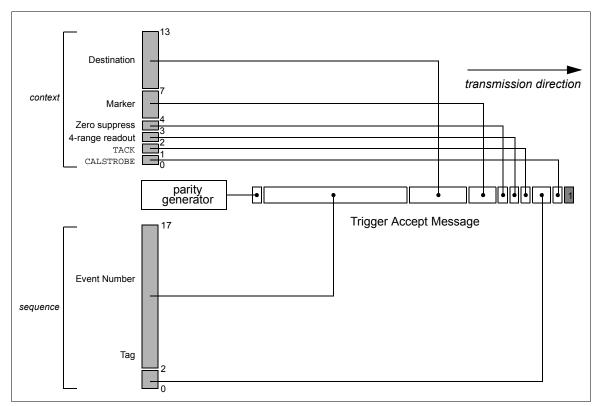

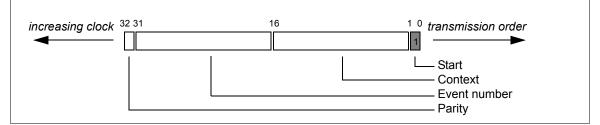

| Figure 40 | p. 64 | Structure of the Trigger Accept Message (TAM)                      |

| Figure 41 | p. 64 | Structure of the Trigger Context                                   |

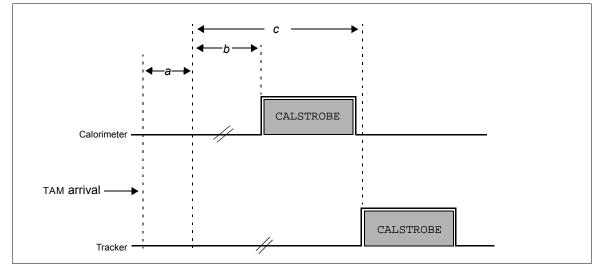

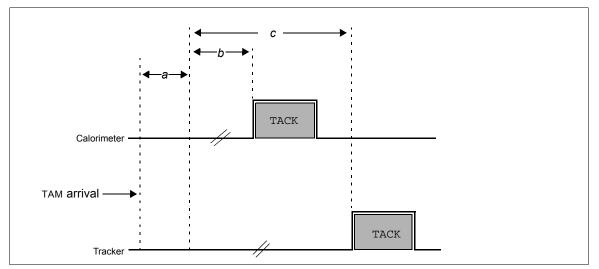

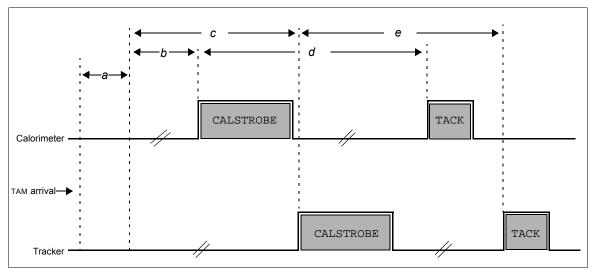

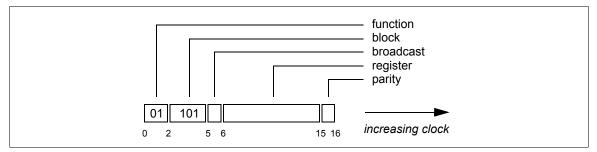

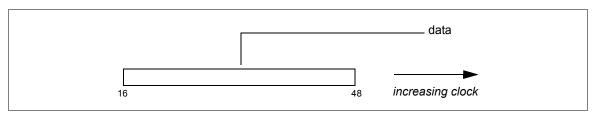

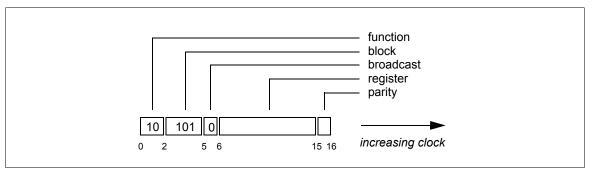

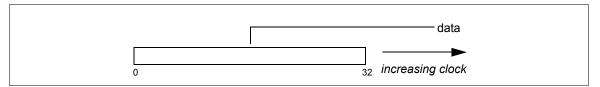

| Figure 42 | p. 67 | TEM trigger Sequence timing for CALSTROBE commands                 |

| Figure 43 | p. 68 | TEM trigger Sequence timing for TACK commands                      |

| Figure 44 | p. 68 | TEM trigger sequence timing for two commands                       |

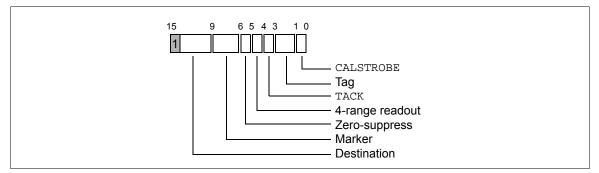

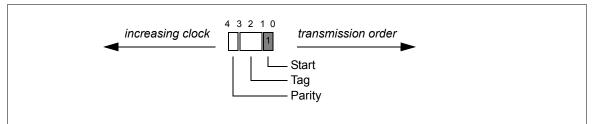

| Figure 45 | p. 69 | Structure of the TACK command for the Calorimeter electronics      |

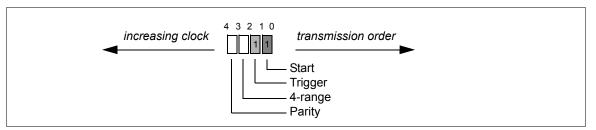

| Figure 46 | p. 70 | Structure of the CALSTROBE command for the Calorimeter electronics |

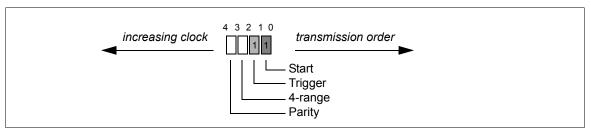

| Figure 47 | p. 70 | Structure of the TACK command for the Tracker electronics          |

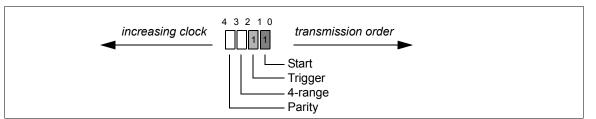

| Figure 48 | p. 70 | Structure of the CALSTROBE command for the Tracker electronics     |

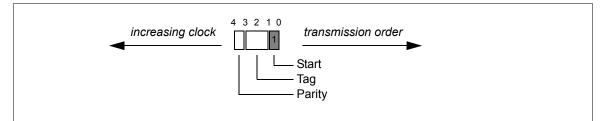

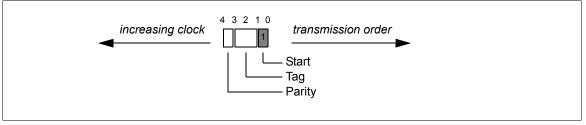

| Figure 49 | p. 71 | Structure of the TACK command for the ACD electronics              |

| Figure 50 | p. 71 | Structure of the CALSTROBE command for the ACD electronics         |

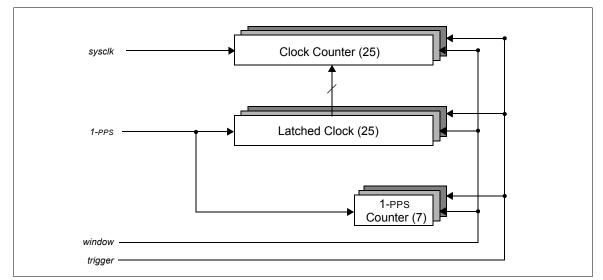

| Figure 51 | p. 72 | Block diagram of the latch and count block of the Timebase         |

| Figure 52 | p. 73 | Round-trip between Trigger Inputs and resulting Trigger            |

| Figure 53 | p. 77 | Configuration register                                             |

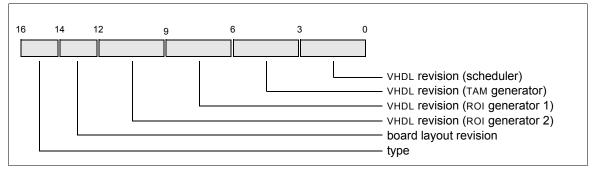

| Figure 54 | p. 78 | Structure of Revision Register or field                            |

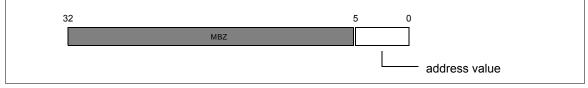

| Figure 55 | p. 79 | Address register                                                   |

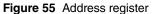

| Figure 56 | p. 80 | The Periodic Trigger Rate register                                 |

| Figure 57 | p. 80 | The periodic mode register                                         |

| Figure 58 | p. 81 | The Limit register                                                 |

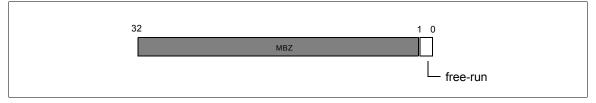

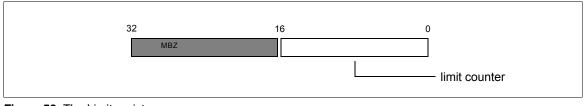

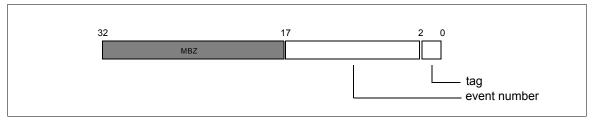

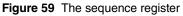

| Figure 59 | p. 81  | The sequence register                                    |

|-----------|--------|----------------------------------------------------------|

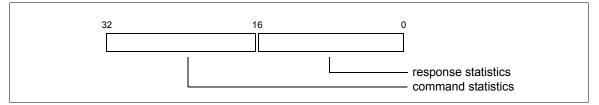

| Figure 60 | p. 82  | The Command/Response statistics register                 |

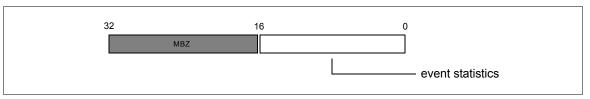

| Figure 61 | p. 82  | The Event statistics register                            |

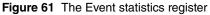

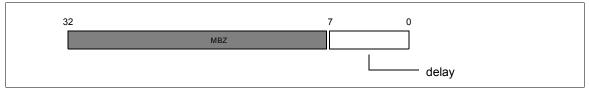

| Figure 62 | p. 83  | External trigger condition delay register                |

| Figure 63 | p. 83  | Window Width register                                    |

| Figure 64 | p. 84  | Window Open Mask register                                |

| Figure 65 | p. 85  | Trigger Accept Message Engine template register          |

| Figure 66 | p. 88  | Livetime statistics register                             |

| Figure 67 | p. 88  | Dead-Zoned register                                      |

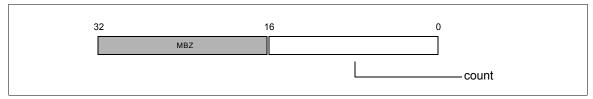

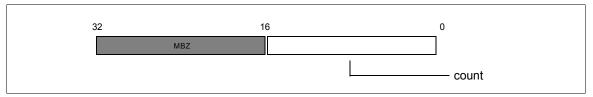

| Figure 68 | p. 89  | Prescaled statistics register                            |

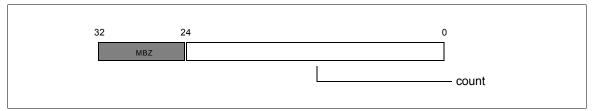

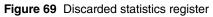

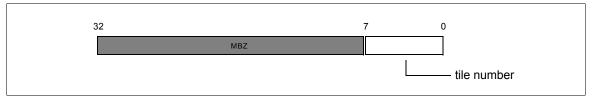

| Figure 69 | p. 89  | Discarded statistics register                            |

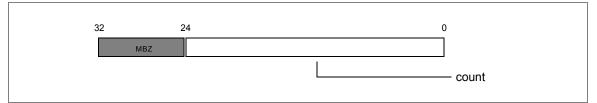

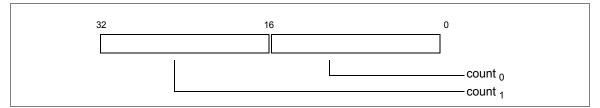

| Figure 70 | p. 89  | Sent statistics register                                 |

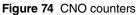

| Figure 71 | p. 90  | Tile counters                                            |

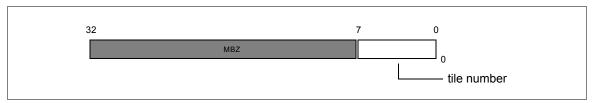

| Figure 72 | p. 90  | Tile to be counted by first tile counter                 |

| Figure 73 | p. 90  | Tile to be counted by second tile counter                |

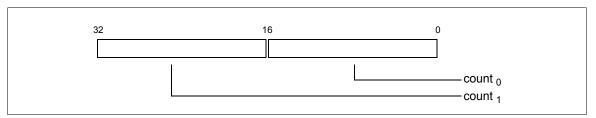

| Figure 74 | p. 91  | CNO counters                                             |

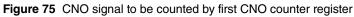

| Figure 75 | p. 91  | CNO signal to be counted by first CNO counter register   |

| Figure 76 | p. 91  | Tile to be counted by second tile counter register       |

| Figure 77 | p. 92  | 1-PPS timing register                                    |

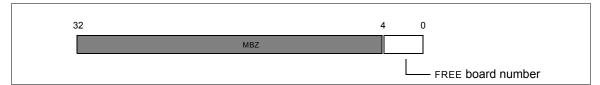

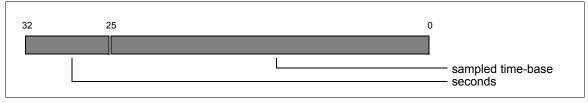

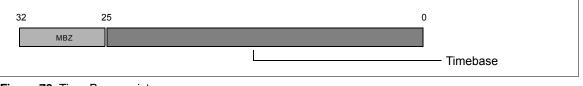

| Figure 78 | p. 92  | Time-Base register                                       |

| Figure 79 | p. 94  | Lookup table (Scheduler register)                        |

| Figure 80 | p. 95  | ROI generator register                                   |

| Figure 81 | p. 96  | Veto and Tower Association mask                          |

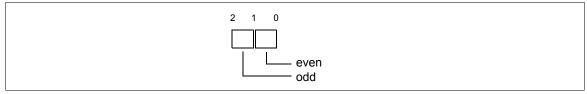

| Figure 82 | p. 96  | Coincidence pair                                         |

| Figure 83 | p. 97  | Veto and coincidence pair association                    |

| Figure 84 | p. 98  | One tower's trigger input masking                        |

| Figure 85 | p. 98  | Towers enable register                                   |

| Figure 86 | p. 99  | ACD CNO enable register                                  |

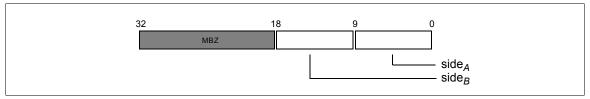

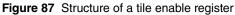

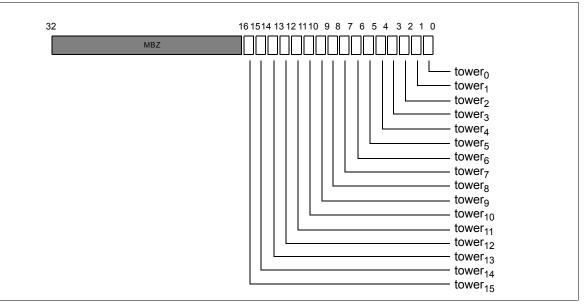

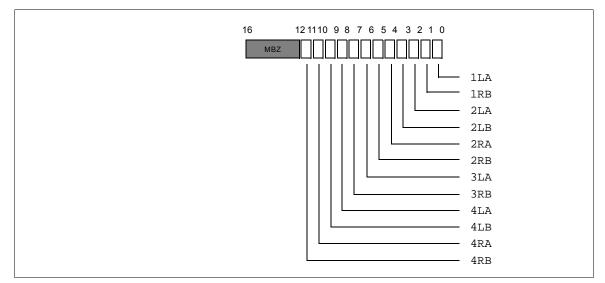

| Figure 87 | p. 99  | Structure of a tile enable register                      |

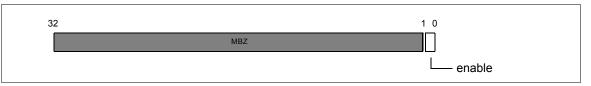

| Figure 88 | p. 106 | Tower busy enable register                               |

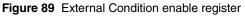

| Figure 89 | p. 106 | External Condition enable register                       |

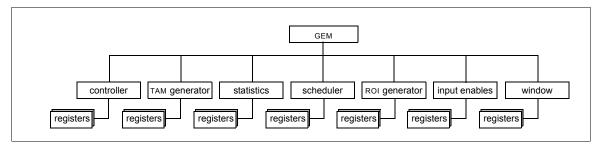

| Figure 90 | p. 107 | Hierarchy of target types                                |

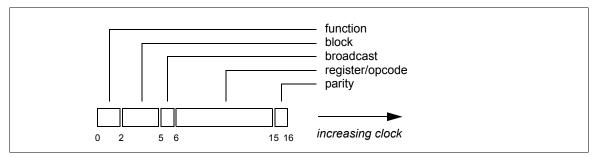

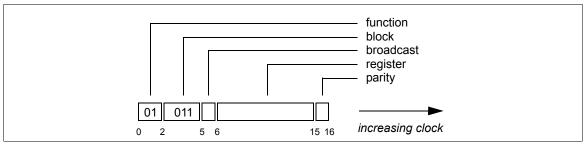

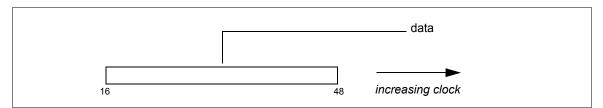

| Figure 91 | p. 108 | GEM access descriptor                                    |

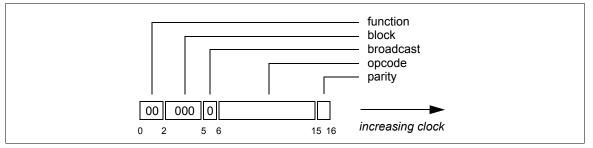

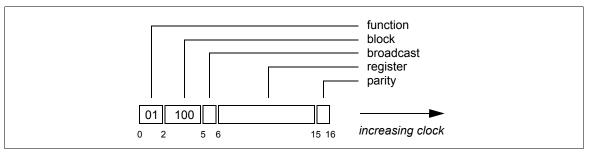

| Figure 92 | p. 109 | Access descriptor for the controller's dataless commands |

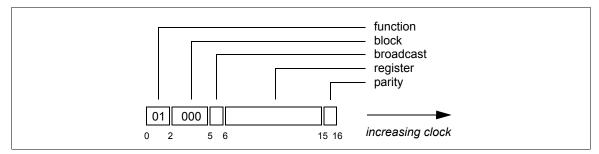

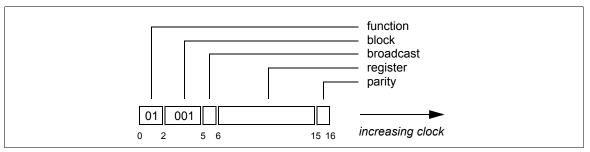

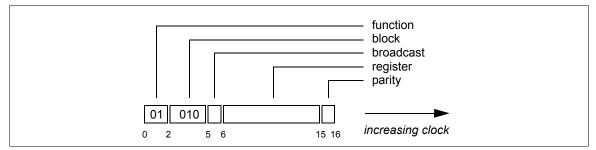

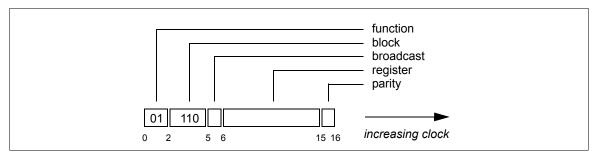

| Figure 93  | p. 109 | Access descriptor for the controller's register load commands        |

|------------|--------|----------------------------------------------------------------------|

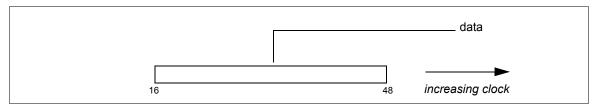

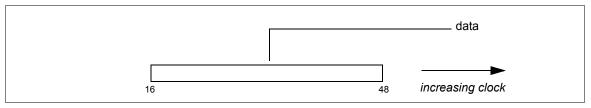

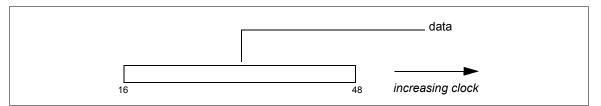

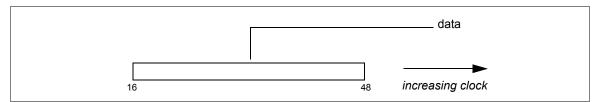

| Figure 94  | p. 110 | Payload for the controller's register load commands                  |

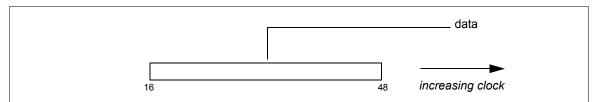

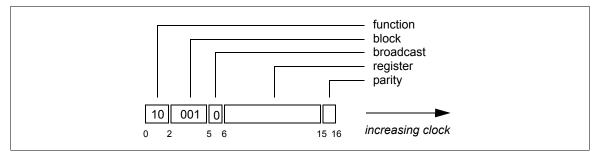

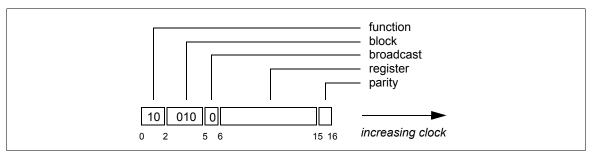

| Figure 95  | p. 110 | Access descriptor for the controller's register read commands        |

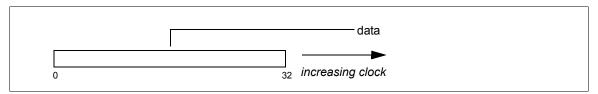

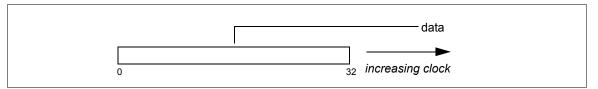

| Figure 96  | p. 110 | Response to a register read command of the controller                |

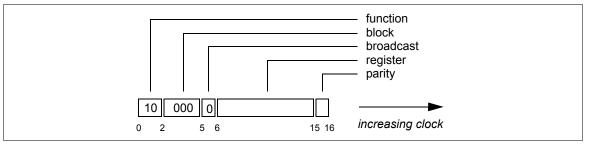

| Figure 97  | p. 111 | Access descriptor for the TAM Generator's register load commands     |

| Figure 98  | p. 111 | Payload for TAM Generator's register load commands                   |

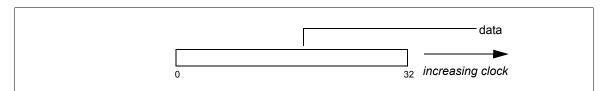

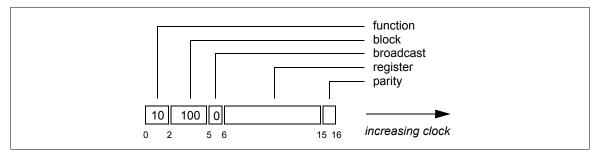

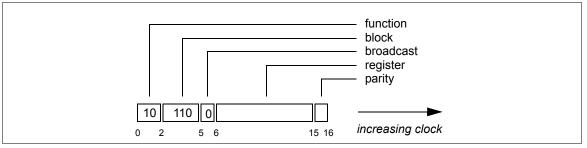

| Figure 99  | p. 111 | Access descriptor for TAM Generator's register read commands         |

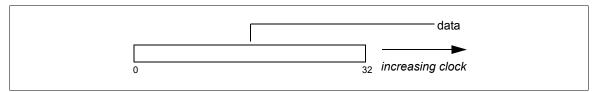

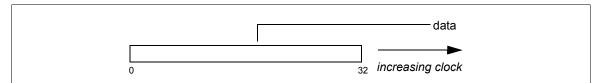

| Figure 100 | p. 112 | Response to register read commands of the TAM Generator              |

| Figure 101 | p. 112 | Access descriptor for the statistics block's register load commands  |

| Figure 102 | p. 112 | Payload for the statistics block's register load commands            |

| Figure 103 | p. 113 | Access descriptor for register read commands of the statistics block |

| Figure 104 | p. 113 | Response to a register read of the statistics block                  |

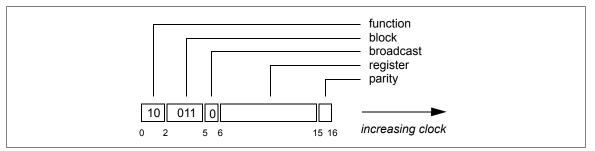

| Figure 105 | p. 113 | Access descriptor for Scheduler register load commands               |

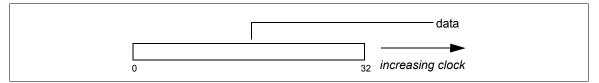

| Figure 106 | p. 114 | Payload for Scheduler register load commands                         |

| Figure 107 | p. 114 | Access descriptor for Scheduler register read commands               |

| Figure 108 | p. 114 | Response to register read commands of the Scheduler                  |

| Figure 109 | p. 115 | Access descriptor for ROI Generator register load commands           |

| Figure 110 | p. 115 | Payload for ROI Generator register load commands                     |

| Figure 111 | p. 115 | Access descriptor for ROI Generator register read commands           |

| Figure 112 | p. 116 | Response to register read commands of the ROI Generator              |

| Figure 113 | p. 116 | Access descriptor for Input Enable register load commands            |

| Figure 114 | p. 116 | Payload for Input Enable register load commands                      |

| Figure 115 | p. 117 | Access descriptor for Input Enable register read commands            |

| Figure 116 | p. 117 | Response to Input Enable register read commands                      |

| Figure 117 | p. 117 | Access descriptor for the window's register load commands            |

| Figure 118 | p. 118 | Payload for the window's register load commands                      |

| Figure 119 | p. 118 | Access descriptor for the window's register read commands            |

| Figure 120 | p. 118 | Response to a register read command of the window block              |

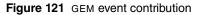

| Figure 121 | p. 119 | GEM event contribution                                               |

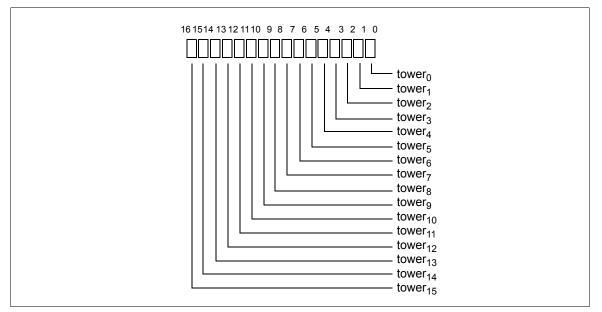

| Figure 122 | p. 120 | ROI Generator contribution to event (ACD used as veto)               |

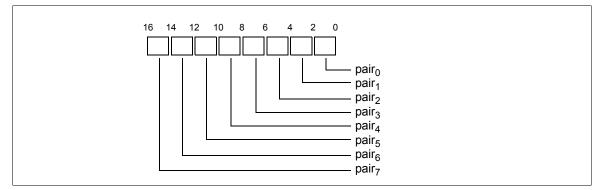

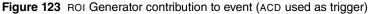

| Figure 123 | p. 121 | ROI Generator contribution to event (ACD used as trigger)            |

| Figure 124 | p. 122 | ACD CNO contribution to event                                        |

| Figure 125 | p. 122 | Condition Summary contribution to event                              |

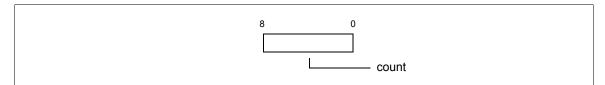

| Figure 126 | p. 123 | Dead-zone counter contribution to event                              |

| Figure 127 | p. 123 | The Veto List contribution to event             |

|------------|--------|-------------------------------------------------|

| Figure 128 | p. 124 | Contribution to event of XZM group in Veto List |

| Figure 129 | p. 124 | Contribution to event of XZP group in Veto List |

| Figure 130 | p. 125 | Contribution to event of YZM group in Veto List |

| Figure 131 | p. 125 | Contribution to event of YZP group in Veto List |

| Figure 132 | p. 126 | Contribution to event of XY group in Veto List  |

| Figure 133 | p. 126 | Contribution to event of RBN group in Veto List |

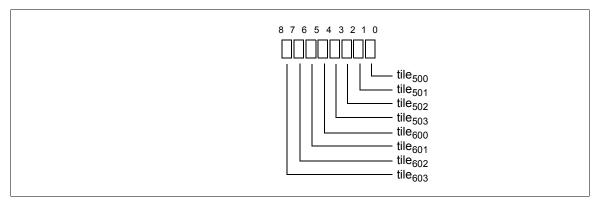

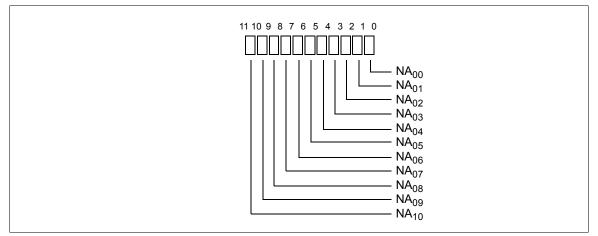

| Figure 134 | p. 127 | Contribution to event of NA group in Veto List  |

| Figure 135 | p. 127 | Livetime contribution to event                  |

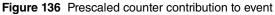

| Figure 136 | p. 127 | Prescaled counter contribution to event         |

| Figure 137 | p. 128 | Discard counter contribution to event           |

| Figure 138 | p. 128 | Sent counter contribution to event              |

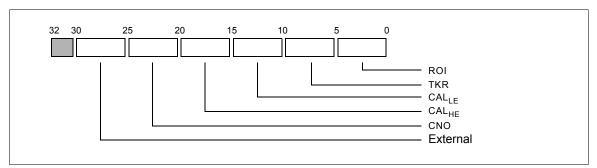

| Figure 139 | p. 129 | Trigger time                                    |

| Figure 140 | p. 129 | 1-PPS timing                                    |

| Figure 141 | p. 130 | Delta event time contribution to event          |

| Figure 142 | p. 130 | Delta window open time contribution to event    |

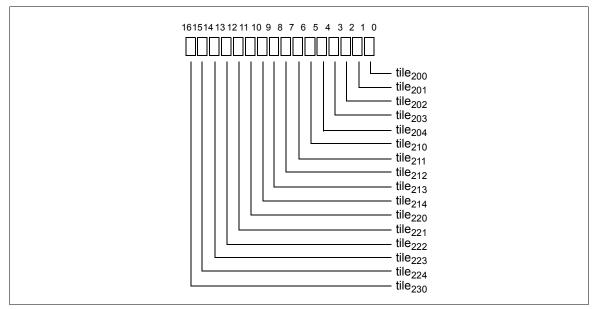

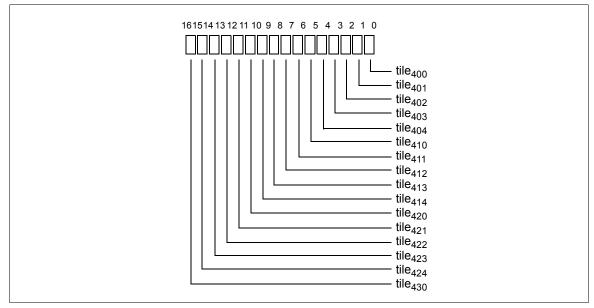

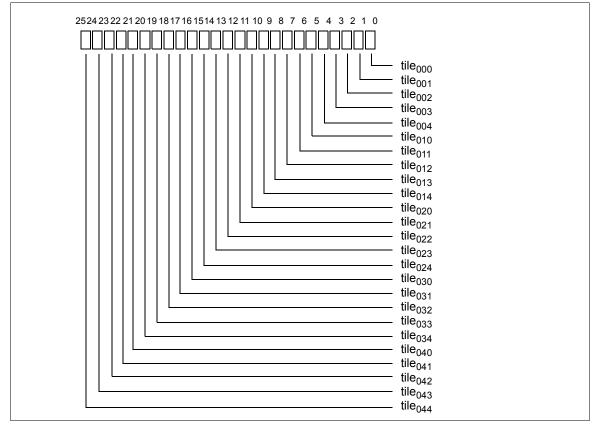

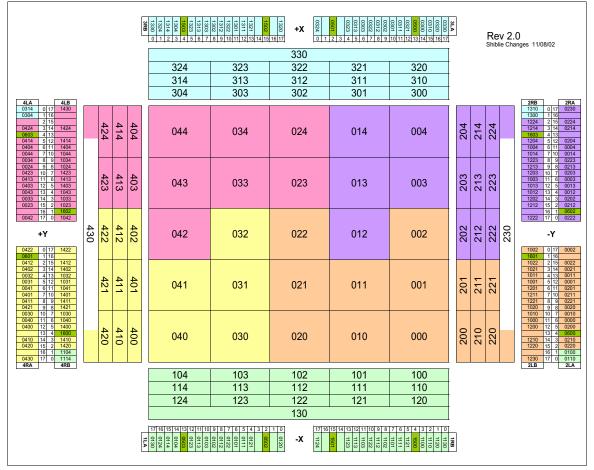

| Figure A.1 | p. 132 | ACD tile mapping                                |

# **List of Tables**

| Table 1  | p. 5   | Document Control Sheet                                     |

|----------|--------|------------------------------------------------------------|

| Table 2  | p. 5   | Approval sheet                                             |

| Table 3  | p. 6   | Document Status Sheet                                      |

| Table 4  | p. 33  | Relationship between FREE board number and FREE board name |

| Table 5  | p. 39  | Possible combinations of TEM "3-in-a-row" Trigger Requests |

| Table 6  | p. 65  | The destination field of the Trigger Accept Message        |

| Table 7  | p. 66  | Response of a module to receiving a Trigger Accept Message |

| Table 8  | p. 76  | The GEM control registers                                  |

| Table 9  | p. 78  | Usage of the type field of the revision register           |

| Table 10 | p. 83  | The GEM control registers                                  |

| Table 11 | p. 85  | The TAM generator registers                                |

| Table 12 | p. 86  | The Trigger Statistics block registers                     |

| Table 13 | p. 93  | The Scheduler registers                                    |

| Table 14 | p. 95  | The ROI Generator registers                                |

| Table 15 | p. 97  | Input enable registers                                     |

| Table 16 | p. 100 | Enables register for tiles 000 through 013                 |

| Table 17 | p. 100 | Enables register for tiles 014 through 032                 |

| Table 18 | p. 101 | Enables register for tiles 33 through NA3                  |

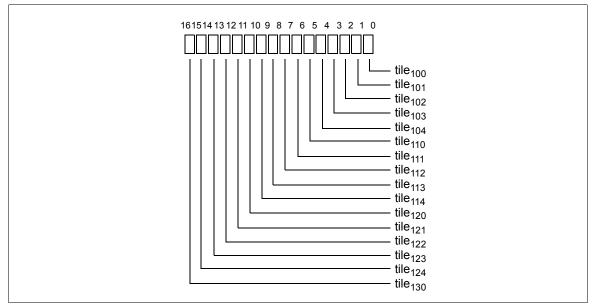

| Table 19 | p. 101 | Enables register for tiles 100 through 113                 |

| Table 20 | p. 102 | Enables register for tiles 114through NA5                  |

| Table 21 | p. 102 | Enables register for tiles 200 through 213                 |

| Table 22 | p. 103 | Enables register for tiles 214 through NA7                 |

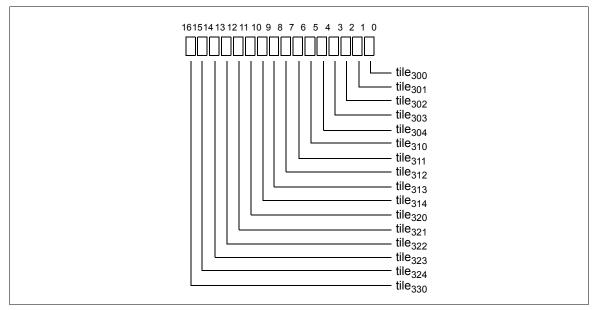

| Table 23 | p. 103 | Enables register for tiles 300 through 313                 |

| Table 24 | p. 104 | Enables register for tiles 314 through NA9                 |

| Table 25  | p. 104 | Enables register for tiles 400 through 413                 |

|-----------|--------|------------------------------------------------------------|

| Table 26  | p. 105 | Enables register for tiles 414 through NA1                 |

| Table 27  | p. 105 | Enables register for tiles 500 through NA10                |

| Table 28  | p. 108 | Block numbers of the GEM                                   |

| Table 29  | p. 109 | The controller's dataless commands                         |

| Table A.1 | p. 132 | Correspondence between tiles, FREE boards, and tile number |

# Chapter 1 Principles of operation

### 1.1 Overview

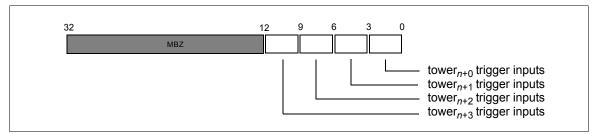

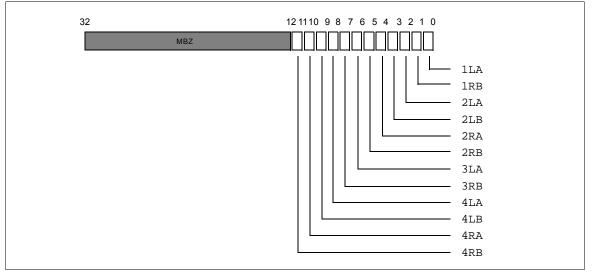

The principal function of the GEM (GLT Electronics Module) is to process *Trigger Inputs* from the LAT'S ACD and sixteen towers and from these signals arrive at a decision on whether or not to *trigger* a readout of detector data. The sum of all the information read out of the detector electronics when triggered is called an *event*.

The ACD's principal function is to reject background in the towers. Thus, from the perspective of the GEM, the primary purpose of the inputs provided by the ACD is as a trigger *veto*. However, to assist in absolute energy calibrations, a second set of signals is developed by the ACD, to be used by the GEM as a *trigger*. Thus, inputs from the ACD fall into two categories:

- **Vetos:** A discriminated signal from each of the 97 tiles of the ACD, used to (potentially) veto tracker triggers originating in any one of the sixteen towers.

- **CNO:** A discriminated and summed signal representing highly ionizing particles from heavy nuclei (Carbon-Nitrogen-Oxygen). This input is used as a trigger.

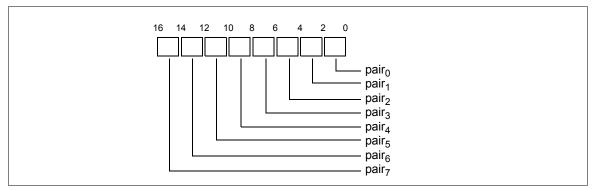

The sixteen towers are identical in composition and each one consists of both tracker and calorimeter systems. Thus, inputs from the towers fall within three categories:

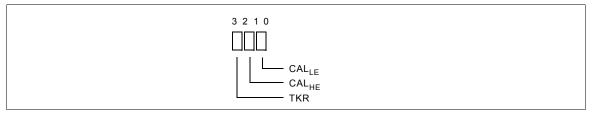

- **TKR:** A three-fold coincidence between any three adjacent *Tracker* layer pairs.

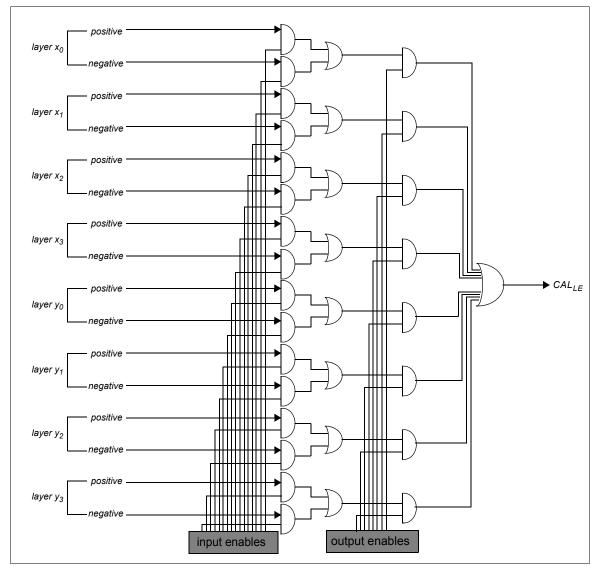

- **CAL (LE):** Deposited energy anywhere within the *Calorimeter* higher than a discriminated value. The calorimeter produces *two* discriminated values: *Low* and *High* energy. This is the *Low* Energy Trigger Input and is referred to as CAL<sub>LE</sub>.

- **CAL (HE):** Deposited energy anywhere within the *Calorimeter* higher than a discriminated value. The calorimeter produces *two* discriminated values: *Low* and *High* energy. This is the *High* Energy Trigger Input and is referred to as CAL<sub>HE</sub>.

And finally, those inputs which are developed in order to both monitor and debug the triggering system itself:

**Periodic:** A periodic, fixed rate signal. The frequency of this signal is derived from either the system clock or the 1-PPS signal.

**Solicited:** This signal is asserted through the Command/Response interface, allowing the system to be triggered through operator intervention.

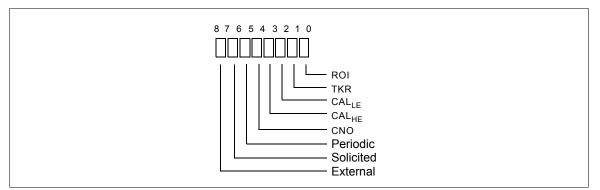

When suitably consolidated by the GEM, these seven different categories also define *trigger conditions*. Each condition corresponds to one reason why the detector should be read out. Conditions are used by the GEM for two different, but equally important functions:

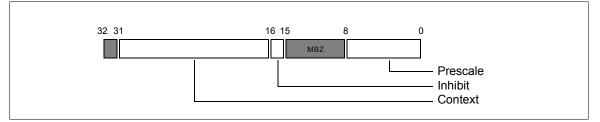

- In order to *open* the *trigger window*. The trigger window defines a period in time in which inputs are defined to be in coincidence. The *width* of this window is a configurable parameter of the GEM. That is, a window is *closed* a fixed time after it is opened. Each time a window is opened and then closed is called a window *turn*.

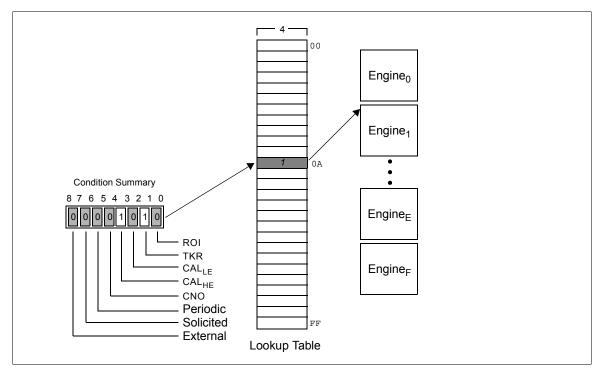

- To determine whether a triggerable *condition* exists in the detector. It's possible, even likely, that more then one condition could be present during the time a window is open. The set of conditions which have occurred between a window opening and closing are a window's *Condition Summary*. As there are eight potential conditions, each window turn could create one of 2<sup>8</sup> (256) possible condition summaries.

Only non-zero condition summaries are candidates for triggering the system. However, a non-zero summary is, in and of itself, not sufficient to guarantee a positive trigger decision and corresponding readout of the LAT. In order to actually trigger a detector readout, a non-zero summary on a window turn must satisfy two additional constraints:

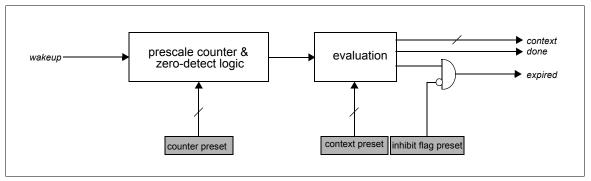

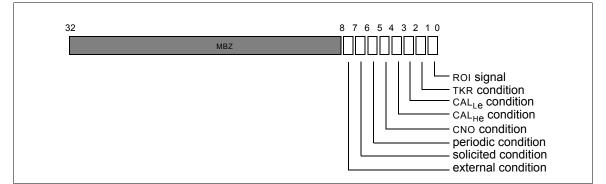

- The *prescaler* associated with the summary must be expired.

- The detector electronics involved in event readout are not busy.

Prescaling allows the user to specify what fraction of the natural rate of the conditions will be passed through the readout of the system. The GEM contains *sixteen* prescalers. The GEM allows its users to associate any of the 127 possible trigger conditions with any one of its sixteen prescalers through the configuration of the *Message Engine lookup table*. The association between Condition Summary and prescale is discussed in 1.7.1.

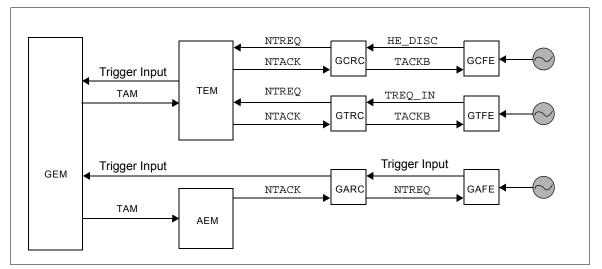

The readout electronics are themselves heavily buffered, and both event readout and event building occur asynchronously with respect to trigger decisions. Because of this, it is entirely possible that a triggerable condition (or conditions) could occur at a time in which the readout electronics would not have the capacity to either absorb or forward the resulting event. In order to deal with this situation, the LAT electronics architecture specifies a flow-control model involving *back-pressure* coupled with a trigger *throttle*. The signal asserted by the readout electronics to the GEM in order to throttle the trigger is called the *busy* signal. A busy signal is asserted to the GEM from both the electronics servicing the sixteen towers (the TEM, or Tower Electronics Module) and the electronics servicing the ACD (the AEM, or ACD Electronics Module).

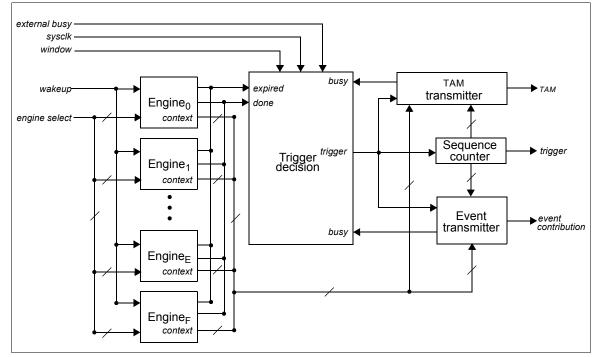

Once the GEM arrives at a decision to read out the LAT, it must communicate this decision to all modules responsible for event readout. It is important to note that it is not just the decision which is broadcast to the modules. In addition, the modules also receive from the GEM, a fixed amount of information which the GEM associates with the decision. This information is called the *Trigger Accept Message*, or TAM. Recipients of this message use its contents to perform destination-specific readout of their respective systems. A discussion on how the GEM determines the contents of a TAM is found in sections 1.8.1 and 1.8.4.

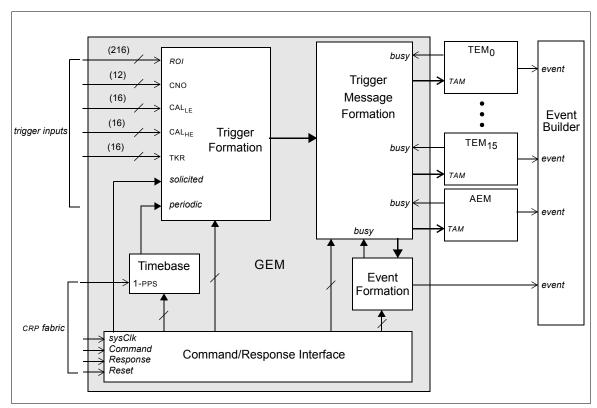

A block diagram of the GEM, its input and output interfaces is illustrated in Figure 1:

Figure 1 The GEM and its input and output interfaces

In this diagram, trigger inputs arrive from the left and are used to both open windows and formulate trigger conditions. A timebase based on the 20 MHZ system clock and 1-PPS signal is used to synthesise the periodic trigger input signal. These candidate triggers are passed to the message formation block, which prescales the candidates and using busy signals from both the TEMs and AEM, determines whether the LAT should be actually triggered and read out. If so, a TAM is broadcast to the TEMs and AEM. These modules will use the message's contents to perform sub-system specific readout of their respective detectors. Eventually this data will be transferred from the module to the EBM (Event Builder Module), where event contributions will be built and subsequently transferred to the L3 filter farm. (See [2].)

Note: The event data path downstream of the GEM is heavily buffered. Consequently, while not readily apparent in the diagram, the transfer of events occurs asynchronously with respect to operation of the GEM.

The GEM contains two other blocks of interest:

**Event Formation:** The GEM itself contributes data to the event. The format and structure of this contribution is described in Chapter 4.

**Command/Response Interface:** The GEM contains a variety of registers. (See Chapter 2.) These registers have two functions: First, they are used to define and specify the configuration of the GEM. Second, they maintain statistics on its operation. In order to access these registers, the GEM appears as a node on the Command/Response fabric. (See [3].) The specific encoding of command and response packets is described in Chapter 3.

### 1.2 Physical partitioning of the GEM

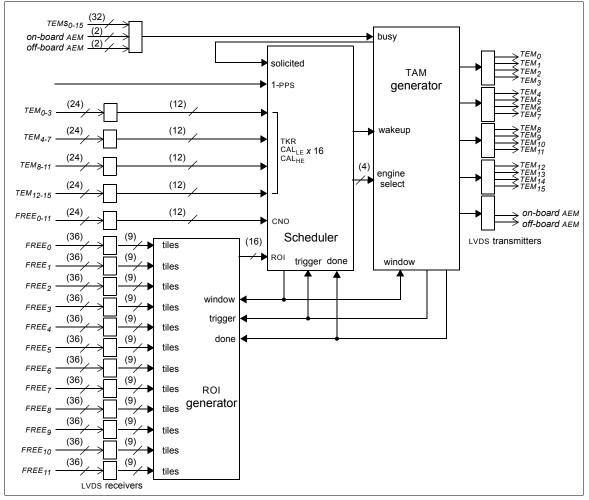

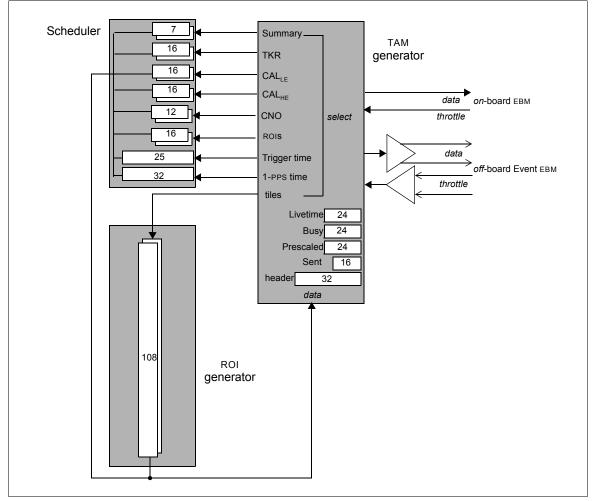

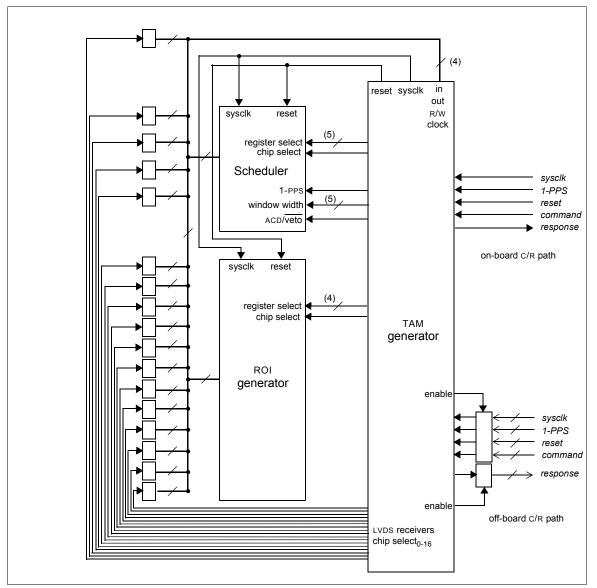

The combinatorial logic necessary to implement the logical blocks described in the previous section (and shown in Figure 1) is distributed over three ACTEL RT54SX series FPGAs. (See [4].) They are named as follows:

- The ROI (Region of Interest) generator

- The Scheduler

- The TAM (Trigger Accept Message) generator

Together, the ROI generator and Scheduler are responsible for trigger formation. The Scheduler also contains the timebase. The TAM generator is responsible for TAM and Event (contribution) formation as well as implementing the Command/Response Interface. In addition to its three FPGAs, the GEM contains 18 copies of a single custom ASIC called the GLTC (GLAST LVDS Translator Chip). This ASIC is used to condition and process LVDS trigger input signals. Finally, there are a number of commercial LVDS transmitters/receivers used to process miscellaneous control and output signals. For pedagogical reasons, these components, their inter-connections, and external I/Os are illustrated through three different diagrams. (See Figures 2, 3, and 4.) Each diagram represents a somewhat disjoint activity on the part of the GEM. For example, Figure 2 illustrates the connectivity to support the pure triggering activity on the part of the GEM, and Figure 4 illustrates the Command/Response Interface to the GEM's registers. By "overlapping" the three diagrams, the totality of the physical implementation of the GEM can be imagined.

Figure 2 Block diagram of the GEM and its trigger paths

Figure 3 Block diagram of the GEM and its event paths

Figure 4 Block diagram of the GEM and its Command/Response paths

The components of the GEM are organized along with the AEM, EBM, and CRU (Command/Response Unit) on a single Printed Circuit Board (PCB) called the DAQ board. The DAQ board resides in the GASU *box* as described in [5]. In actuality, in order to satisfy redundancy requirements there are *two* DAQ boards, both identical and both residing in the same GASU box. One board is referred to as the *primary* DAQ board and the other as the *redundant* DAQ board. The GEM on the primary DAQ board is called the *primary* GEM and the GEM on the redundant DAQ board, the *redundant* GEM. In typical operation, only one of two DAQ boards is powered; consequently, only one of two GEMs can operate at any one time. However, the operating GEM can be either the primary or redundant module.

### 1.3 Trigger Sources

#### 1.3.1 The ACD